# ANALOG ELECTRONICS

# AIM & OBJECTIVES:

- To acquaint the students with construction, theory and characteristics of P-N junction diode

- Analyze the different application of diodes

- To familiarize the student with the analysis and modelling of diode.

- Understand the characteristics of transistors.

- Design and analyze various rectifier and amplifier circuits. Design sinusoidal and nonsinusoidal oscillators.

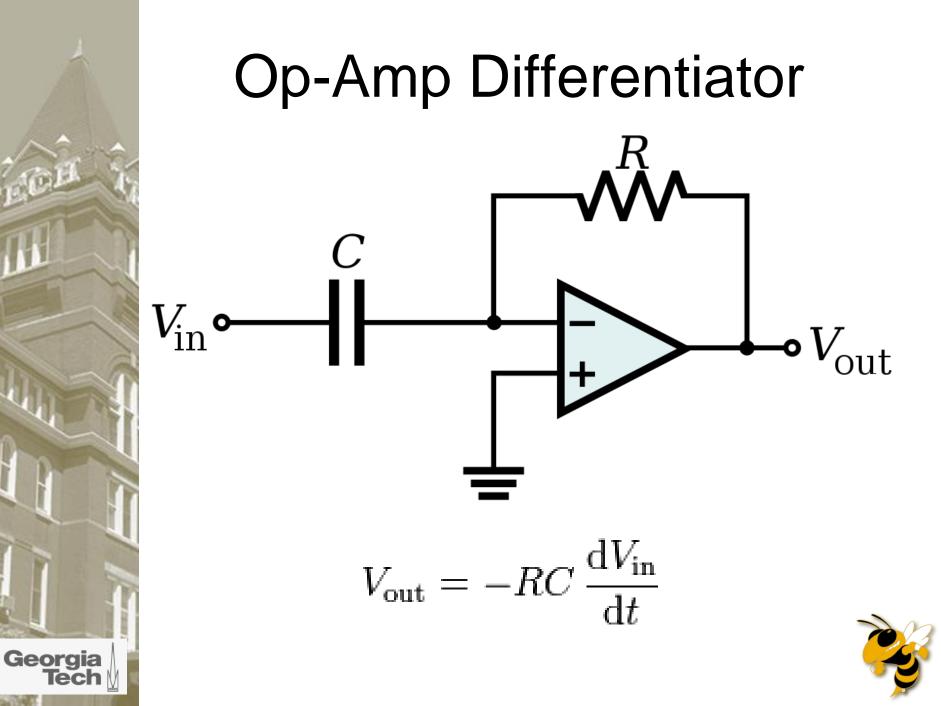

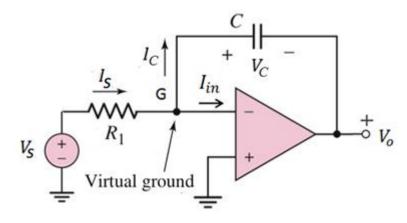

- Understand the functioning of OP-AMP and design OP-AMP based circuits.

# PRE TEST

1. What is the barrier potential of a Silicon diode and Germanium Diode at room temperature?

- a) Si=0.3, Ge=0.7 b) Si=0.7, Ge=1

- c) Si=1, Ge=0.3

- d) Si=0.7, Ge=0.3

- 2. Which is the most widely used semiconductor?

- a) Copper

- b) Germanium

- c) Silicon

- d) None of the above

- 3. The depletion region or space charge region or transition region in a semiconductor p-n junction diode has

- a) Electrons and holes.

- b) Positive ions and electrons.

- c) Positive and negative ions.

- d) Negative ions and holes

- 4. In a P-N junction the positive voltage at which the diode starts to conduct consequently is called.

- a) Cut off voltage

- b) Saturation voltage

- c) Knee voltage

- d) Breakdown voltage

- 5. A diode

- a) Is the simplest of the semiconductor devices

- b) Has a characteristic that closely follows that of a switch

- c) Is two terminal device

- d) All of the mentioned

- 6. The emitter current  $I_E$  in a transistor is 3mA. If the leakage current  $I_CBO$  is 5µA and  $\alpha$ =0.98, calculate the collector and base current.

- a) 3.64mA and 35 $\mu A$

b) 2.945mA and  $55\mu A$

- c) 3.64mA and 33 $\mu A$

- d) 5.89mA and  $65\mu A$

- 7. In CB configuration, the value of  $\alpha$ =0.98A. A voltage drop of 4.9V is obtained across the resistor of 5K $\Omega$  when connected in collector circuit. Find the base current.

- a) 0.01mA

- b) 0.07mA

- c) 0.02mA

- d) 0.05mA

- 8. For a MOSFET Vgs=3V, Idss=5A, and Id=2A. Find the pinch of voltage Vp

- a) 4.08

- b) 8.16

- c) 16.32 d) 0V

- 9. The approximate input impedance of the opamp circuit which has Ri = 10k, Rf = 100k, RL = 10k

- a)∞

b) 120k

- c)110k

- d) 10k

- 10. Calculate the frequency of oscillation for RC phase shift oscillator having the value of R and C as  $5\Omega$  and  $7\mu$ F respectively.

- a) 1230 Hz

- b) 1857 Hz

- c) 502Hz

- d) 673 Hz

# **PREREQUISITE** :

- Knowledge about PN junction, biasing

- Should know about circuit analysis.

# **MODULE I - DIODE CIRCUITS**

# **INTRODUCTION**

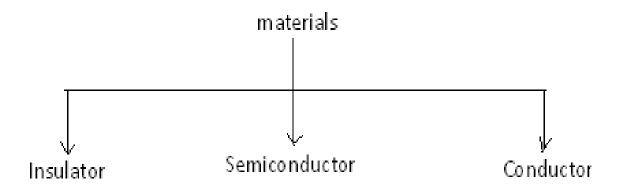

Based on the electrical conductivity all the materials in nature are classified as insulators, Semiconductors, and conductors

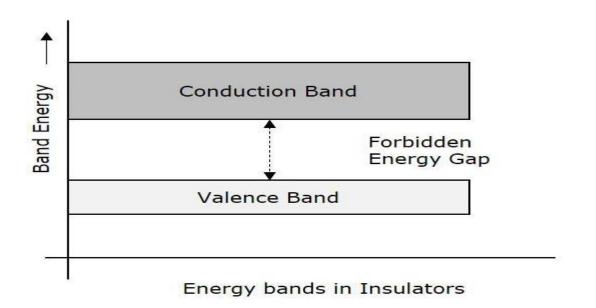

# **INSULATOR**

An insulatorisamaterialthatoffersaverylow level (or negligible) of conductivity when voltage is applied.

- Eg:Paper,Mica,glass,quartz.

- Typical resistivity level of an insulator is of the order of 1010 to 1012  $\Omega$ -cm.

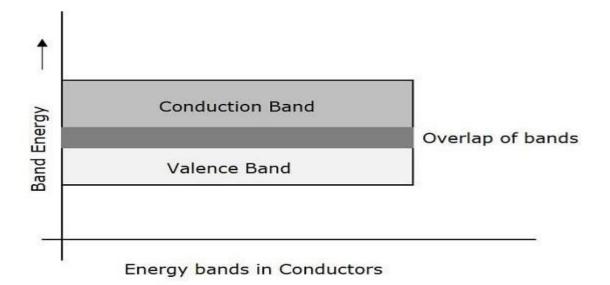

# CONDUCTOR

- A conductor isamaterial which supports a generous flow of charge when avoltage is applied across terminals.i.e. it has very high conductivity.

- Eg:Copper,Aluminum,Silver, Gold.

- The resistivity of a conductor is in the order of  $10^{-4}$  and  $10^{-6}\Omega$ -cm.

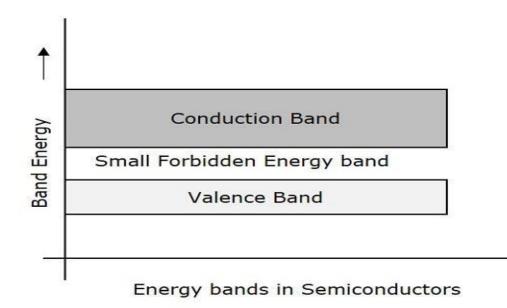

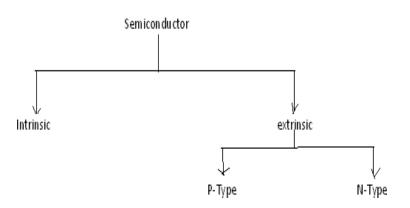

# SEMICONDUCTOR

- A semiconductor is a material that has its conductivity somewhere between the insulator and conductor.

- The resistivity level is in the range of 10and104  $\Omega$ -cm.

- Two of the most commonly used are Silicon (Si=14 atomic no.) and germanium (Ge=32 atomic no.).

# INTRINSIC SEMICONDUCTOR

- Apureformofsemiconductorsiscalledas intrinsic semiconductor. Conduction in intrinsic semiconductor is either due to thermalexcitationorcrystaldefects.

- Si and Ge are the two most important semiconductors used. Other examples include Gallium arsenide GaAs, Indium Antimonide (InSb)etc.

# EXTRINSIC SEMICONDUCTOR

- Intrinsic semiconductor hasverylimited applications as they conduct very small amounts of current at room temperature.

- The current conduction capability of intrinsic semiconductorcanbeincreased significantlybyadding a small amounts impurity to the intrinsic semiconductor.

- By adding impurities it becomes impure or extrinsic semiconductor. This process of adding impurities called as doping.

- The amount of impurity added is 1 part in  $10^6$  atoms.

# **N-TYPE SEMICONDUCTOR**

- If the added impurity is a pentavalent atom then the resultant semiconductor is called N- type semiconductor.

- Examples of pentavalent impurities are Phosphorus, Arsenic, Bismuth, Antimony etc

# **P-TYPE SEMICONDUCTOR**

- If the added impurity is a trivalent atom then the resultant semiconductor is called P-type semiconductor.

- Examples of trivalent impurities are Boron, Gallium, indiumetc.

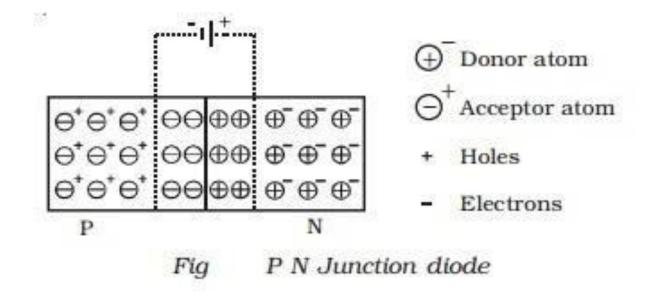

# **PN JUNCTION**

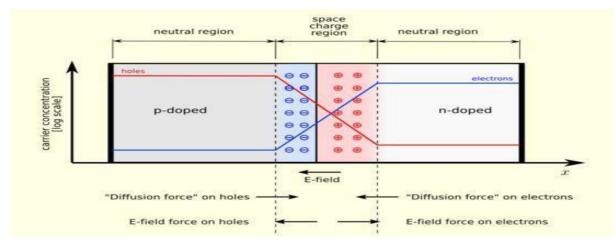

- In a piece of semiconductor, if one half is doped by ptype impurity and theother half is doped by n type impurity, a PN junction is formed.

- The plane dividing the twohalves or zones is called PNjunction.

- At the junction there is a tendency of free electrons to diffuse over to the Pside and the holes to the N side. This process is called diffusion.

- As the free electrons move across the junction from N type to P type, the donor atoms become positively charged.

- Hence a positive charge is built on the N-side of the junction. The free electrons that cross the junction uncover the negative acceptor ions by filing the holes. Therefore a negative charge is developed on the p- side of the junction.

- This net negative charge on the p side preventsfurtherdiffusion of electrons into the p side.

- SimilarlythenetpositivechargeontheNside repelstheholecrossingfrompsidetoNside.

- Thusabarriersissetupnearthejunction which prevents the further movement of charge carriers i.e. electrons and holes.

- An electrostatic potential difference is established between P and N regions, which are called the potential barrier, junction barrier, diffusion potential or contact potential, Vo.

- The magnitude of the contact potential Vovaries with doping levels and temperature. Vois 0.3 V for Ge and 0.72 V for Si.

- The junction region is depleted of mobile charge carriers. Hence it is called depletion layer, space region, and transition region.

- The depletion region is of the order of  $0.5\mu m$  thick. There are no mobile carriers in this narrow depletion region.

- Hencenocurrentflowsacrossthejunctionand the systemis in equilibrium.

- To the left of this depletion layer, the carrier concentrationisp=NA and to its right it is n=ND.

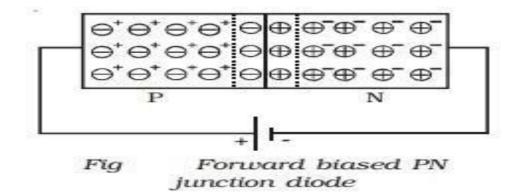

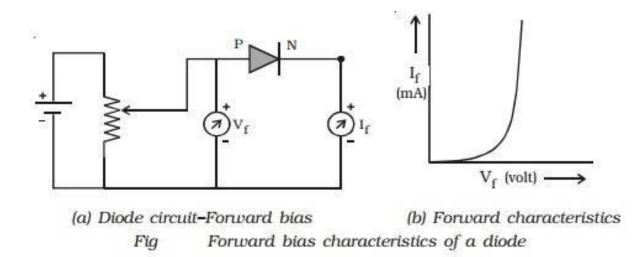

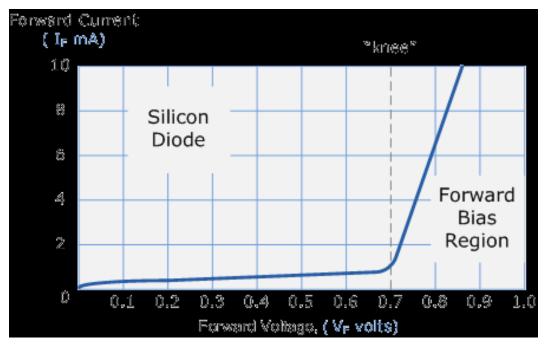

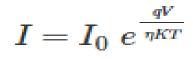

### FORWARD BIASED JUNTION

- When a diode is connected in a Forward Bias condition, a negative voltage is applied to the Ntype material and apositive voltage is applied to the P-type material.

- If this external voltage becomes greater than the value of the potential barrier, approx.0.7 volts for silicon and 0.3 volts for germanium, the potential barriers opposition will be overcome and current will start to flow.

- This is because the negative voltagepushesorrepelselectronstowards the junction giving them the energy to cross over and combine with the holes being pushed in the opposite direction towards the junction by the positive voltage.

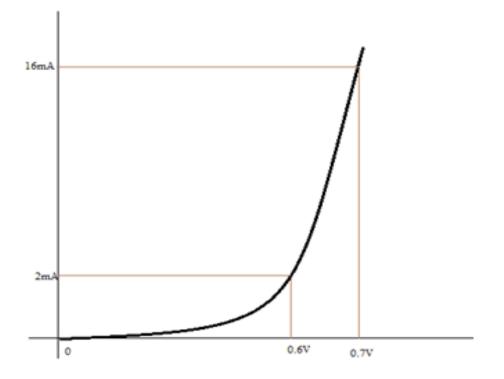

# Forward Characteristics Curve for a Junction Diode

This results in a characteristics curve of zero current flowing up to this voltage point, called the "knee" on the static curves and then a high current flow through the diode with little increase in the external voltage.

# FORWARD BIASED JUNCTION DIODE

- The application of a forward biasing voltage on the junction diode results in the depletion layer becoming very thin and narrow which represents a low impedance path through the junction thereby allowing high currents to flow.

- The point at which this sudden increase in current takes place is represented on the static I-V characteristics curve above as the "knee" point.

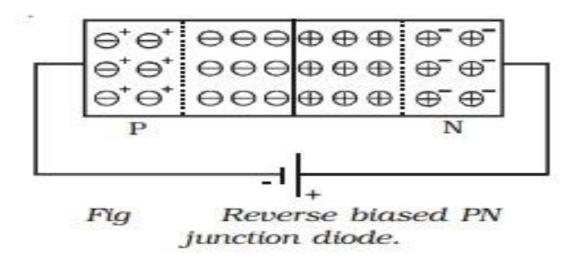

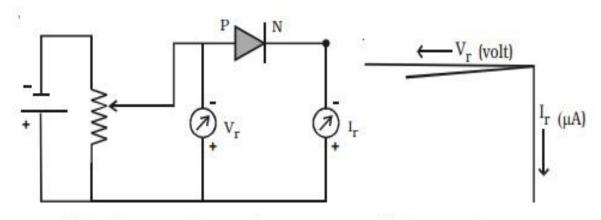

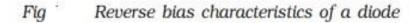

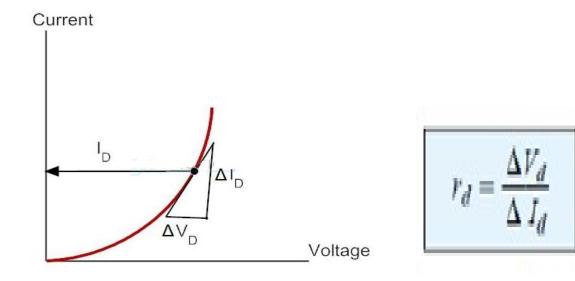

### **REVERSEBIASED JUNCTION**

- When a diode is connected in a Reverse Bias condition, a positive voltage is applied to the N-type material and a negative voltage is applied to the P-type material.

- The positive voltage applied to the N-type material attracts electrons towards the positive electrode and away from the junction, while the holes in the P-type end are also attracted away from the junction towards the negative electrode.

- The net result is that the depletion layer grows wider due to a lack of electrons and holes and presents a high impedance path, almost an insulator. The result is that a high potential barrier is created thus preventing current from flowing through the semiconductor material.

- This condition represents a high resistance value to the PN junction and practically zero current flows through the junction diode with an increase in bias voltage. However, a very small **leakage current** does flow through the junction which can be measured in microamperes,  $(\mu A)$ .

- One final point, if the reverse bias voltage Vr applied to the diode is increased to a sufficiently high enough value, it will cause the PN junction to overheat and fail due to the avalanche effect around the junction. This may cause the diode to become shorted and will result in the flow of maximum circuit current, and this shown as a step downward slope in the reverse static characteristics curve.

(a) Diode circuit-Reverse bias

(b) Reverse characteristics

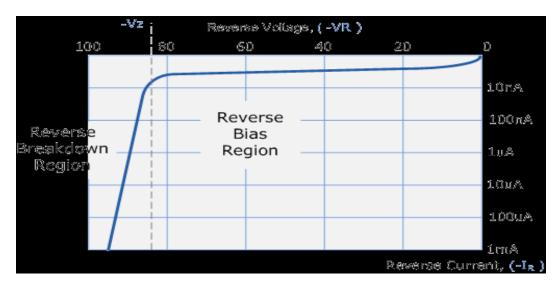

**DIODE CURRENT EQUATION**

Where

- I Diode Current

- Io- Diode reverse saturation current at room temperature

- V- External Voltage applied to the diode

- $\eta-A$  constant, 2- Silicon and 1- Germanium

- k-Boltzmann's constant,  $1.38066{\times}~10^{\text{-}23}J/K$

- q- charge of an electron,  $1.60219 \times 10^{-19} C$

- T- temperature of the diode junction

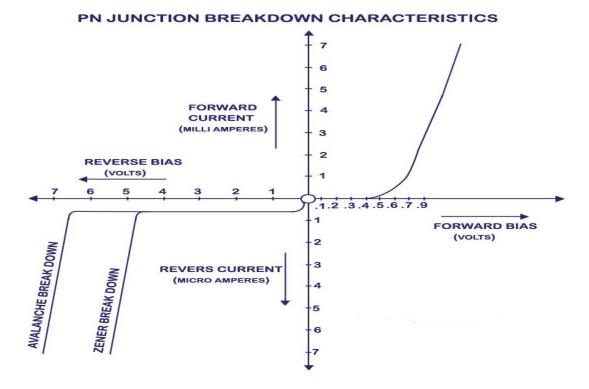

### **V-I CHARACTERISTICS**

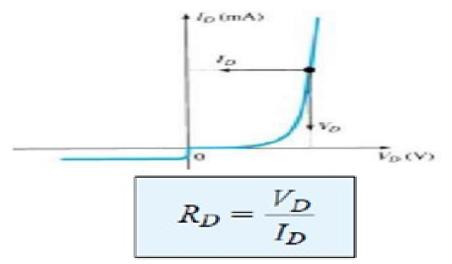

# **RESISTANCE LEVELS:** DC or Static Resistance:

The application of a dc voltage to a circuit containing a semiconductor diode will result in an operating point on the characteristic curve that will not change with time. The resistance of the diode at the operating point can be found simply by finding the corresponding levels of VD and ID.

# AC or DYNAMIC RESISTANCE:

- If a sinusoidal input is applied, the situation will change completely. The varying input will move the instantaneous operating point up and down a region of the characteristics and thus defines a specific change in current and voltage.

- A straight-line drawn tangent to the curve through the Q-point will define a particular change in voltage and current that can be used to determine the ac or dynamic resistance.

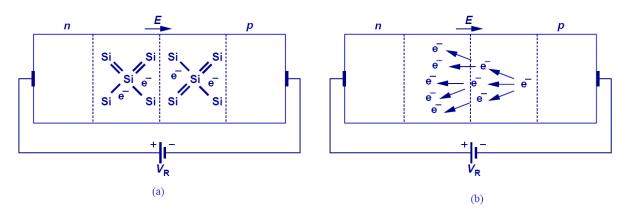

# **BREAK DOWN MECHANISMS:**

#### Avalanche breakdown

• The minority carriers, under reverse biased conditions, flowing through the junction acquire a kinetic energy which increases with the increase in reverse voltage. At a sufficiently high reverse voltage (say 5 V or more), the kinetic energy of minority carriers becomes so large that they knock out electrons from the covalent bonds of the semiconductor material. As a result of collision, the liberated electrons in turn liberate more electrons and the current becomes very large leading to the breakdown of the crystal structure itself. This phenomenon is called the avalanche breakdown. *The breakdown* region is the knee of the characteristic curve. Now the current is not controlled by the junction voltage but rather by the external circuit.

#### Zener breakdown

- Under a very high reverse voltage, the depletion region expands and the potential barrier increases leading to a very high electric field across the junction. The electric field will break some of the covalent bonds of the semiconductor atoms leading to a large number of free minority carriers, which suddenly increase the reverse current. This is called the Zener effect.

- The breakdown occurs at a particular and constant value of reverse voltage called the breakdown voltage, it is found that Zener breakdown occurs at electric field intensity of about 3 x 107 V/m.

#### Zener vs Avalanche Breakdown:

- Zener breakdown is a result of the large electric field inside the depletion region that breaks electrons or holes off their covalent bonds.

- Avalanche breakdown is a result of electrons or holes colliding with the fixed ions inside the depletion region.

# **BREAK DOWN MECHANISMS**

# **RECTIFIERS:**

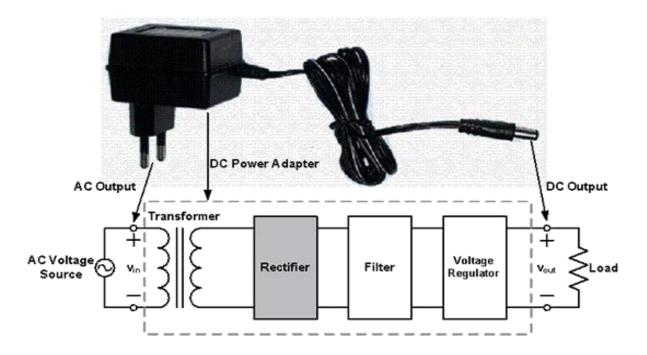

**Block Diagram of Regulated power Supply**

# **Rectification:**

• Rectification is a process of converting the alternating quantity (voltage or current) into a corresponding direct quantity(voltage or current).

• The input to a rectifier is AC whereas its output is unidirectional or DC.

# **Need of Rectification**

- Every electronic circuit such as amplifiers, needs a DC power source for its operation.

- This DC voltage has to be obtained from AC supply.

• For this the AC supply has to be reduced Stepped down first using a Step down transformer and then converted to dc by using rectifier.

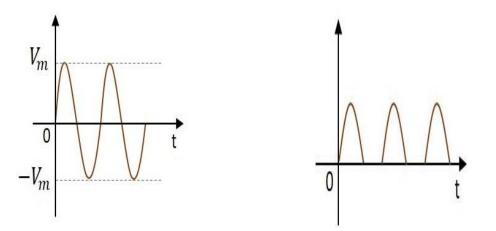

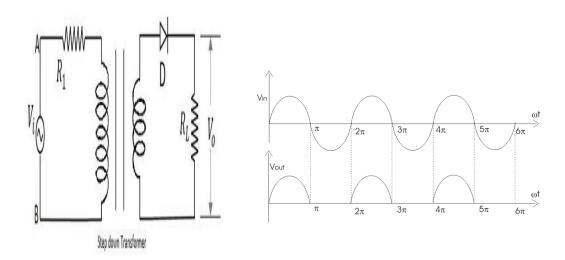

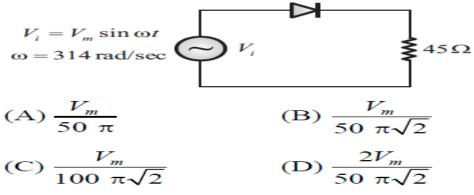

# Half Wave Rectifier:

### **Operation:**

- A Half-wave rectifier circuit rectifies only positive half cycles of the input supply .

- The AC signal is given through an input transformer which steps up or down according to the usage. Mostly a step down transformer is used in rectifier circuits, so as to reduce the input voltage.

- The input signal given to the transformer is passed through a PN junction diode which acts as a rectifier. This diode converts the AC voltage into pulsating dc for only the positive half cycles of the input. A load resistor is connected at the end of the circuit.

- This diode gets ON conducts for positive half cycles of input signal. Hence a current flows in the circuit and there will be a voltage drop across the load resistor. This output will be pulsating DC which is taken across the load resistor.

The diode gets OFF doesn't conduct for negative half cycles and hence the output for negative half cycles will be, iD=0 and Vo=0

#### Analysis of Half-Wave Rectifier:

To analyze a half-wave rectifier circuit, let us consider the equation of input voltage.

$$v_i = V_m \sin \omega t$$

$V_m$  is the maximum value of supply voltage.

Let us assume that the diode is ideal.

- $^{

abla}$  The resistance in the forward direction, i.e., in the ON state is  $\ R_{f}$  .

- $^{

abla}$  The resistance in the reverse direction, i.e., in the OFF state is  $\ R_r$  .

The current **i** in the diode or the load resistor  $R_L$  is given by

$$egin{array}{lll} i = I_m \sin \omega t & for & 0 \leq \omega t \leq 2\pi \ i = 0 & for & \pi \leq \omega t \leq 2\pi \end{array}$$

Where

$$I_m = rac{V_m}{R_f + R_L}$$

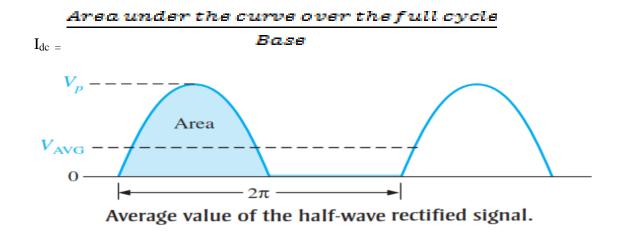

# **DC Output Current:**

• The average current  $I_{dc}$  is given by

**DC Output Current**

$$\begin{split} I_{dc} &= \frac{1}{2\pi} \int_{0}^{2\pi} i \, d \, (\omega t) \\ &= \frac{1}{2\pi} \left[ \int_{0}^{\pi} I_{m} \sin \omega t \, d \, (\omega t) + \int_{0}^{2\pi} 0 \, d \, (\omega t) \right] \\ &= \frac{1}{2\pi} [I_{m} \{ -\cos \omega t \}_{0}^{\pi}] \\ &= \frac{1}{2\pi} [I_{m} \{ +1 - (-1) \}] = \frac{I_{m}}{\pi} = 0.318 I_{m} \end{split}$$

Substituting the value of  $\ I_m$  , we get

$$I_{dc} = rac{V_m}{\pi \left( R_f + R_L

ight)}$$

If  $\ R_L >> R_f$  , then

$$I_{dc}=rac{V_m}{\pi R_L}=0.318rac{V_m}{R_L}$$

# **DC Output Voltage:**

The DC output voltage is given by

$$egin{aligned} V_{dc} &= I_{dc} imes R_L = rac{I_m}{\pi} imes R_L \ &= rac{V_m imes R_L}{\pi \left(R_f + R_L

ight)} = rac{V_m}{\pi \left\{1 + \left(R_f/R_L

ight)

ight\}} \end{aligned}$$

If  $oldsymbol{R}_L>>oldsymbol{R}_f$  , then

$$V_{dc}=rac{V_m}{\pi}=0.318V_m$$

**RMS** Current and Voltage:

The value of RMS current is given by

$$\begin{split} I_{rms} &= \left[\frac{1}{2\pi}\int_{0}^{2\pi}i^{2}d\left(\omega t\right)\right]^{\frac{1}{2}}\\ I_{rms} &= \left[\frac{1}{2\pi}\int_{0}^{2\pi}I_{m}^{2}\sin^{2}\omega t\,d\left(\omega t\right) + \frac{1}{2\pi}\int_{\pi}^{2\pi}0\,d\left(\omega t\right)\right]^{\frac{1}{2}}\\ &= \left[\frac{I_{m}^{2}}{2\pi}\int_{0}^{\pi}\left(\frac{1-\cos 2\omega t}{2}\right)d\left(\omega t\right)\right]^{\frac{1}{2}}\\ &= \left[\frac{I_{m}^{2}}{4\pi}\left\{\left(\omega t\right) - \frac{\sin 2\omega t}{2}\right\}_{0}^{\pi}\right]^{\frac{1}{2}}\\ &= \left[\frac{I_{m}^{2}}{4\pi}\left\{\pi - 0 - \frac{\sin 2\pi}{2} + \sin 0\right\}\right]^{\frac{1}{2}}\\ &= \left[\frac{I_{m}^{2}}{4\pi}\right]^{\frac{1}{2}} = \frac{I_{m}}{2} \end{split}$$

RMS voltage across the load is

$$V_{rms}=I_{rms} imes R_L=rac{V_m imes R_L}{2\,(R_f+R_L)}$$

$=rac{V_m}{2\,\{1+(R_f/R_L)\}}$  $R_f$  , then

If  $oldsymbol{R}_L>>oldsymbol{R}_f$  , then

$$V_{rms}=rac{V_m}{2}$$

#### **Rectifier Efficiency:**

Any circuit needs to be efficient in its working for a better output. To calculate the efficiency of a half wave rectifier, the ratio of the output power to the input power has to be considered. The rectifier efficiency is defined as

$$\eta = rac{d.\,c.\,power\,\,delivered\,\,to\,\,the\,\,load}{a.\,c.\,input\,\,power\,\,from\,\,transformer\,\,secondary} = rac{P_{ac}}{P_{dc}}$$

Now

$$P_{dc} = (I_{dc})^2 imes R_L = rac{I_m R_L}{\pi^2}$$

Further

$$P_{ac} = P_a + P_r$$

Where

$P_a = power \ dissipated \ at \ the \ junction \ of \ diode$

$$=I_{rms}^2 imes R_f=rac{I_m^2}{4} imes R_f$$

$P_r = power \ dissipated \ in \ the \ load \ resistance$

$$=I_{rms}^2 imes R_L=rac{I_m^2}{4} imes R_L$$

$P_{ac}=rac{I_m^2}{4} imes R_f+rac{I_m^2}{4} imes R_L=rac{I_m^2}{4}(R_f+R_L)$

From both the expressions of  $\ P_{ac}$  and  $\ P_{dc}$  , we can write

$$\begin{split} \eta &= \frac{I_m^2 R_L / \pi^2}{I_m^2 \left(R_f + R_L\right) / 4} = \frac{4}{\pi^2} \frac{R_L}{\left(R_f + R_L\right)} \\ &= \frac{4}{\pi^2} \frac{1}{\left\{1 + \left(R_f / R_L\right)\right\}} = \frac{0.406}{\left\{1 + \left(R_f / R_L\right)\right\}} \end{split}$$

Percentage rectifier efficiency

$$\eta = rac{40.6}{\{1 + (\,R_f/R_L)\,\}}$$

#### **Ripple Factor:**

- The rectified output contains some amount of AC component present in it, in the form of ripples. This is understood by observing the output waveform of the half wave rectifier. To get a pure dc, we need to have an idea on this component.

- The ripple factor gives the waviness of the rectified output. It is denoted by **y**. This can be defined as the ratio of the effective value of ac component of voltage or current to the direct value or average value.

And

$$\gamma = \frac{ripple \ voltage}{d. \ c \ voltage} = \frac{rms \ value \ of \ a. \ c. \ component}{d. \ c. \ value \ of \ wave} = \frac{(V_r)_{rms}}{v_{dc}}$$

Here,

$$(V_r)_{rms}=\sqrt{V_{rms}^2-V_{dc}^2}$$

Therefore,

$$\gamma = rac{\sqrt{V_{rms}^2 - V_{dc}^2}}{V_{dc}} = \sqrt{\left(rac{V_{rms}}{V_{dc}}

ight)^2 - 1}$$

Now,

$$\begin{split} V_{rms} &= \left[\frac{1}{2\pi} \int_{0}^{2\pi} V_{m}^{2} \sin^{2} \omega t \, d\left(\omega t\right)\right]^{\frac{1}{2}} \\ &= V_{m} \left[\frac{1}{4\pi} \int_{0}^{\pi} \left(1 - \cos 2 \, \omega t\right) d\left(\omega t\right)\right]^{\frac{1}{2}} = \frac{V_{m}}{2} \\ V_{dc} &= V_{av} = \frac{1}{2\pi} \left[\int_{0}^{\pi} V_{m} \sin \omega t \, d\left(\omega t\right) + \int_{0}^{2\pi} 0.d\left(\omega t\right)\right] \\ &= \frac{V_{m}}{2\pi} [-\cos \omega t]_{0}^{\pi} = \frac{V_{m}}{\pi} \\ &= \sqrt{\left[\left\{\frac{\left(V_{m}/2\right)}{\left(V_{m}/\pi\right)}\right\}^{2} - 1\right]} = \sqrt{\left\{\left(\frac{\pi}{2}\right)^{2} - 1\right\}} = 1.21 \end{split}$$

The ripple factor is also defined as

$\gamma$

$$\gamma = rac{(I_r)_{rms}}{I_{dc}}$$

As the value of ripple factor present in a half wave rectifier is 1.21, it means that the amount of a.c. present in the output is 121% of the d.c. voltage

#### **Regulation:**

- The current through the load may vary depending upon the load resistance. But even at such condition, we expect our output voltage which is taken across that load resistor, to be constant. So, our voltage needs to be regulated even under different load conditions.

- The variation of D.C. output voltage with change in D.C. load current is defined as the **Regulation**.

- The lower the percentage regulation, the better would be the power supply. An ideal power supply will have a zero percentage regulation.

- The percentage regulation is calculated as follows.

$$Percentage \ regulation = rac{V_{no \ load} - V_{full \ load}}{V_{full \ load}} imes 100\%$$

#### **Transformer Utilization Factor:**

The D.C. power to be delivered to the load, in a rectifier circuit decides the rating of the transformer used in a circuit.

So, the transformer utilization factor is defined as

$$TUF = rac{d.\,c.\,power\ to\ be\ delivered\ to\ the\ load}{a.\,c.\ rating\ of\ the\ transformer\ secondary}$$

$$=rac{P_{d.c}}{P_{a.c(rated)}}$$

According to the theory of transformer, the rated voltage of the secondary will be

$V_m/\sqrt{2}$

The actual R.M.S. voltage flowing through it will be

$$I_m/2$$

Therefore

$$TUF = rac{\left(I_m/\pi

ight)^2 imes R_L}{\left(V_m/\sqrt{2}

ight) imes \left(I_m/2

ight)}$$

But

Therefore

$$V_m = I_m \left( R_f + R_L \right)$$

$$TUF = rac{(I_m/\pi)^2 imes R_L}{\{I_m \left(R_f + R_L

ight)/\sqrt{2}

ight\} imes (I_m/2)}$$

$= rac{2\sqrt{2}}{\pi^2} imes rac{R_L}{(R_f + R_L)}$

$= rac{2\sqrt{2}}{\pi^2} = 0.287$

#### **Peak Inverse Voltage:**

• A diode when connected in reverse bias, should be operated under a controlled level of voltage. If that safe voltage is exceeded, the diode gets damaged. Hence it is very important to know about that maximum voltage.

- The maximum inverse voltage that the diode can withstand without being destroyed is called as **Peak Inverse Voltage**. In short, **PIV**.

- Here the PIV is nothing but Vm

### **Form Factor:**

• This can be understood as the mathematical mean of absolute values of all points on the waveform. The **form factor** is defined as the ratio of R.M.S. value to the average value. It is denoted by **F**.

$$F=rac{rms\ value}{average\ value}=rac{I_m/2}{I_m/\pi}=rac{0.5I_m}{0.318I_m}=1.57$$

#### **Peak Factor:**

- The value of peak in the ripple has to be considered to know how effective the rectification is. The value of peak factor is also an important consideration. **Peak factor** is defined as the ratio of peak value to the R.M.S. value.

- Therefore

$$PeakFactor = rac{Peak\,value}{r.\,m.\,s\,value} = rac{V_m}{V_m/2} = 2$$

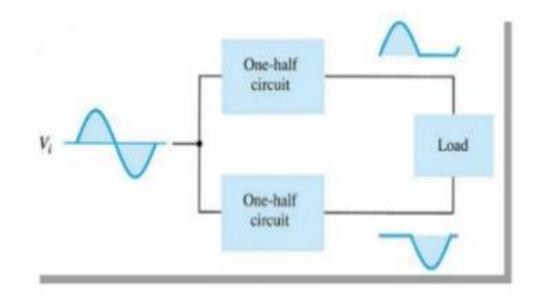

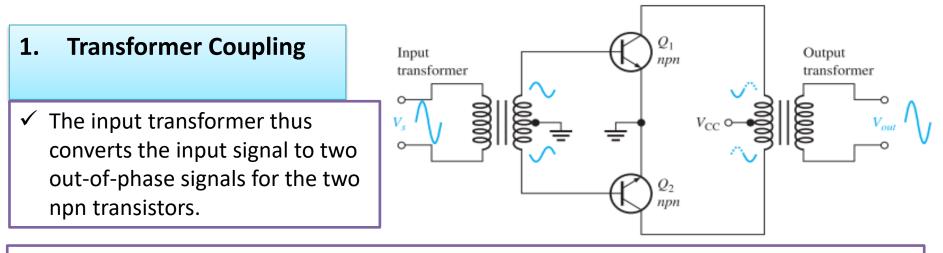

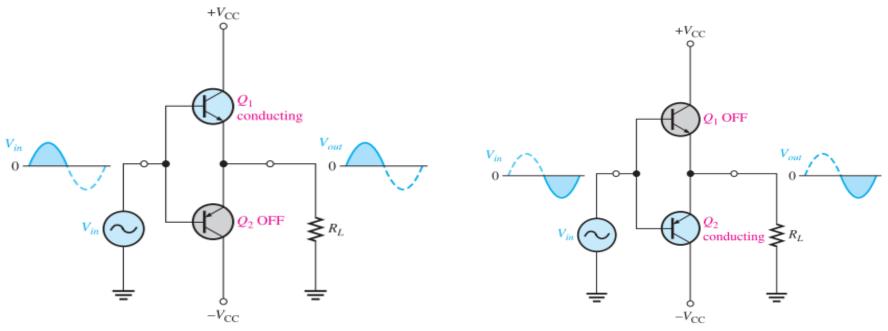

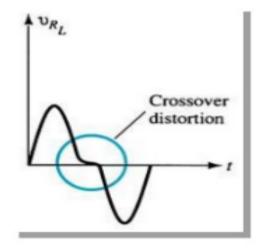

#### **Full-Wave Rectifier:**

- A Rectifier circuit that rectifies both the positive and negative half cycles can be termed as a full wave rectifier as it rectifies the complete cycle. The construction of a full wave rectifier can be made in two types. They are

- Center-tapped Full wave rectifier

- Bridge full wave rectifier

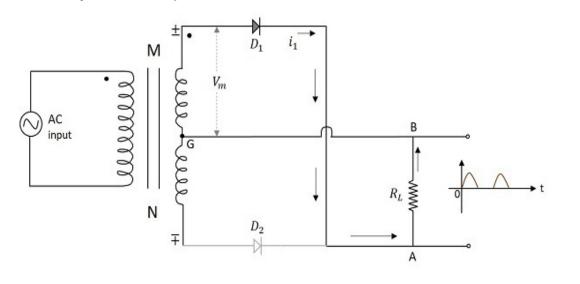

#### **Center-tapped Full-Wave Rectifier:**

• A rectifier circuit whose transformer secondary is tapped to get the desired output voltage, using two diodes alternatively, to rectify the complete cycle is called as a **Center-tapped Full wave rectifier circuit**.

- The features of a center-tapping transformer are –

- The tapping is done by drawing a lead at the mid-point on the secondary winding. This winding is split into two equal halves by doing so.

- The voltage at the tapped mid-point is zero. This forms a neutral point.

- The center tapping provides two separate output voltages which are equal in magnitude but opposite in polarity to each other.

- A number of tapings can be drawn out to obtain different levels of voltages.

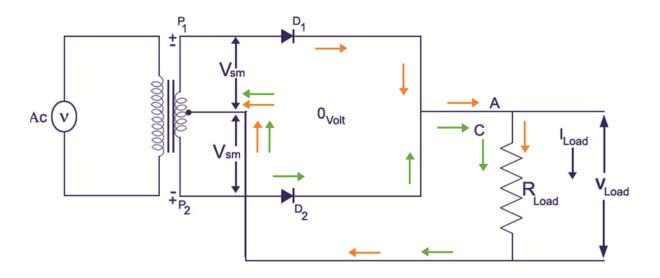

#### Working:

The working of a center-tapped full wave rectifier can be understood by the above figure. When the positive half cycle of the input voltage is applied, the point M at the transformer secondary becomes positive with respect to the point N. This makes the diode  $D_1$  forward

biased. Hence current  $i_1$  flows through the load resistor from A to B. We now have the positive half cycles in the output

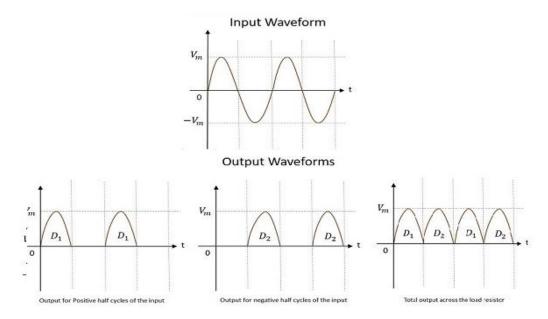

# Waveforms of CT FWR:

The input and output waveforms of the center-tapped full wave rectifier are as follows.

From the above figure it is evident that the output is obtained for both the positive and negative half cycles. It is also observed that the output across the load resistor is in the **same direction** for both the half cycles.

#### **Peak Inverse Voltage:**

• As the maximum voltage across half secondary winding is V<sub>m</sub>, the whole of the secondary voltage appears across the non-conducting diode. Hence the **peak inverse voltage** is twice the maximum voltage across the half-secondary winding, i.e.

# $PIV = 2V_m$

#### **Disadvantages:**

- There are few disadvantages for a center-tapped full wave rectifier such as -

- Location of center-tapping is difficult

- The dc output voltage is small

- PIV of the diodes should be high

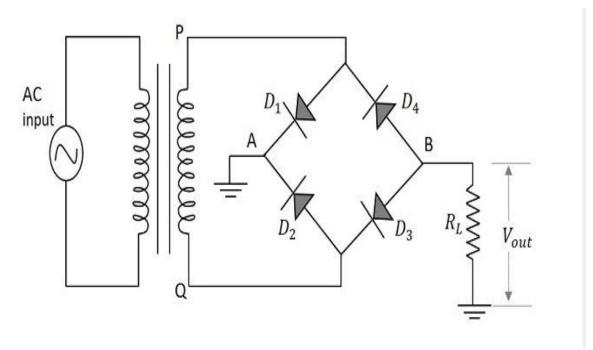

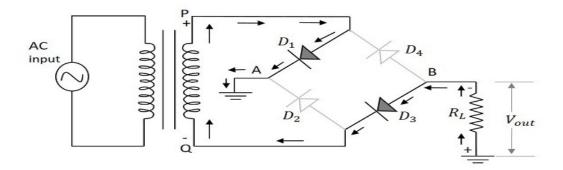

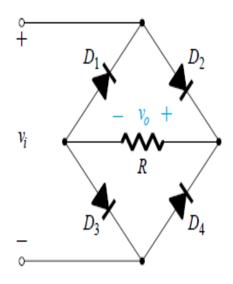

#### **Bridge Full-Wave Rectifier:**

• It utilizes four diodes connected in bridge form so as not only to produce the output during the full cycle of input, but also to eliminate the disadvantages of the center-tapped full wave rectifier circuit.

• There is no need of any center-tapping of the transformer in this circuit. Four diodes called D<sub>1</sub>, D<sub>2</sub>, D<sub>3</sub>and D<sub>4</sub> are used in constructing a bridge type network so that two of the diodes conduct for one half cycle and two conduct for the other half cycle of the input supply.

#### Working:

The full wave rectifier with four diodes connected in bridge circuit is employed to get a better full wave output response. When the positive half cycle of the input supply is given, point P becomes positive with respect to the point  $\mathbf{Q}$ . This makes the diode  $D_1$  and  $D_3$  forward biased while  $D_2$  and  $D_4$  reverse biased. These two diodes will now be in series with the load resistor.

The following figure indicates this along with the conventional current flow in the circuit.

• Hence the diodes D<sub>2</sub> and D<sub>4</sub> conduct during the negative half cycle of the input supply to produce the output along the load resistor. Here also two diodes work to produce the output voltage. The current flows in the same direction as during the positive half cycle of the input.

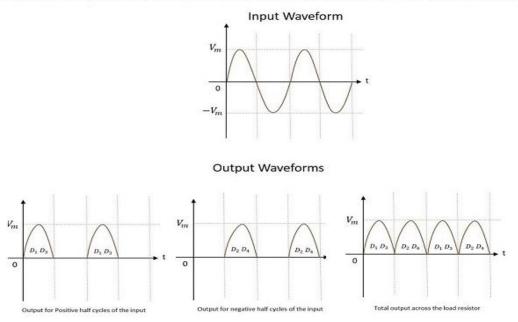

#### Waveforms:

The input and output waveforms of the center-tapped full wave rectifier are as follows.

From the above figure, it is evident that the output is obtained for both the positive and negative half cycles. It is also observed that the output across the load resistor is in the **same direction** for both the half cycles.

#### **Peak Inverse Voltage:**

• Whenever two of the diodes are being in parallel to the secondary of the transformer, the maximum secondary voltage across the transformer appears at the non-conducting diodes which makes the PIV of the rectifier circuit. Hence the **peak inverse voltage** is the maximum voltage across the secondary winding, i.e.

$$PIV = V_m$$

#### Advantages:

- There are many advantages for a bridge full wave rectifier, such as -

- No need of center-tapping.

- The dc output voltage is twice that of the center-tapper FWR.

- PIV of the diodes is of the half value that of the center-tapper FWR.

- The design of the circuit is easier with better output.

#### Analysis:

In order to analyze a full wave rectifier circuit, let us assume the input voltage  $\ V_i$  as,

$$V_i = V_m \sin \omega t$$

The current  $\,\,i_1\,\,$  through the load resistor  $\,\,R_L\,\,$  is given by

$$egin{array}{lll} i_1 = I_m \sin \omega t & for & 0 \leq \omega t \leq \pi \ i_1 = & 0 & for & \pi \leq \omega t \leq 2\pi \end{array}$$

Where

$$I_m = rac{V_m}{R_f + R_L}$$

$R_f$  being the diode resistance in ON condition.

Similarly, the current  $i_2$  flowing through diode  $D_2$  and load resistor RL is given by,

$$i_2= 0 \qquad for \quad 0 \leq \omega t \leq \pi$$

$$i_2 = I_m \sin \omega t \quad for \quad \pi \leq \omega t \leq 2\pi$$

The total current flowing through  $R_L$  is the sum of the two currents  $i_1$  and  $i_2$  i.e.

$$i = i_1 + i_2$$

#### **D.C. or Average Current:**

The average value of output current that a D.C. ammeter will indicate is given by

$$=rac{I_m}{\pi}+rac{I_m}{\pi}=rac{2I_m}{\pi}=0.636I_m$$

This is double the value of a half wave rectifier.

# **D.C. Output Voltage:**

The dc output voltage across load is given by

$$V_{dc} = I_{dc} \times R_L = \frac{2I_m R_L}{\pi} = 0.636 I_m R_L$$

Thus the dc output voltage is twice that of a half wave rectifier.

# **RMS Current**:

The RMS value of the current is given by

$$I_{rms} = \left[rac{1}{\pi}\int_{0}^{\pi}t^{2}\,d\left(\omega t

ight)

ight]^{rac{1}{2}}$$

Since current is of the two same form in the two halves

$$=\left[rac{I_m^2}{\pi}\int_0^{\pi}\sin^2\omega t\,d\left(\omega t

ight)

ight]^{rac{1}{2}}$$

$$=\frac{I_m}{\sqrt{2}}$$

# **Rectifier Efficiency:**

The rectifier efficiency is defined as

$$\eta = rac{P_{dc}}{P_{ac}}$$

Now,

$$P_{dc} = (V_{dc})^2/R_L = (2V_m/\pi)^2$$

And,

$$P_{ac} = (V_{rms})^2 / R_L = (V_m / \sqrt{2})^2$$

Therefore,

$$\eta = rac{P_{dc}}{P_{ac}} = rac{\left( 2 V_m / \pi

ight)^2}{\left( V_m / \sqrt{2}

ight)^2} = rac{8}{\pi^2}$$

$$= 0.812 = 81.2\%$$

# **Ripple Factor:**

The form factor of rectified output voltage of a full wave rectifier is given by

$$F = rac{I_{rms}}{I_{dc}} = rac{I_m/\sqrt{2}}{2I_m/\pi} = 1.11$$

The ripple factor  $\gamma$  is defined as usingaccircuit theory

$$egin{aligned} &\gamma = \left[ \left( rac{I_{rms}}{I_{dc}}

ight) - 1

ight]^rac{1}{2} = \left( F^2 - 1

ight)^rac{1}{2} \ &= \left[ (1.11)^2 - 1

ight]^rac{1}{2} = 0.48 \end{aligned}$$

This is a great improvement over the half wave rectifier's ripple factor which was 1.21 **Regulation**:

The dc output voltage is given by

$$V_{dc} = \frac{2I_m R_L}{\pi} = \frac{2V_m R_L}{\pi \left(R_f + R_L\right)}$$

$$=\frac{2V_m}{\pi}\left[1-\frac{R_f}{R_f+R_L}\right]=\frac{2V_m}{\pi}-I_{dc}R_f$$

# **Transformer Utilization Factor:**

The TUF of a half wave rectifier is 0.287

There are two secondary windings in a center-tapped rectifier and hence the TUF of centertapped full wave rectifier is

$$(TUF)_{avg} = rac{P_{dc}}{V-A \ rating \ of \ a \ transformer}$$

$$=\frac{(TUF)_p + (TUF)_s + (TUF)_s}{3}$$

$$=\frac{0.812+0.287+0.287}{3}=0.693$$

| Terms                | Half Wave Rectifier | Center Tapped FWR | Bridge FWR     |

|----------------------|---------------------|-------------------|----------------|

| Number of Diodes     | 1                   | 2                 | 4              |

| Transformer tapping  | No                  | Yes               | No             |

| Peak Inverse Voltage | $V_m$               | $2V_m$            | $V_m$          |

| Maximum Efficiency   | 40.6%               | 81.2%             | 81.2%          |

| Average / dc current | $I_m/\pi$           | $2I_m/\pi$        | $2I_m/\pi$     |

| DC voltage           | $V_m/\pi$           | $2V_m/\pi$        | $2V_m/\pi$     |

| RMS current          | $I_m/2$             | $I_m/\sqrt{2}$    | $I_m/\sqrt{2}$ |

| Ripple Factor        | 1.21                | 0.48              | 0.48           |

| Output frequency     | $f_{in}$            | $2f_{in}$         | $2f_{in}$      |

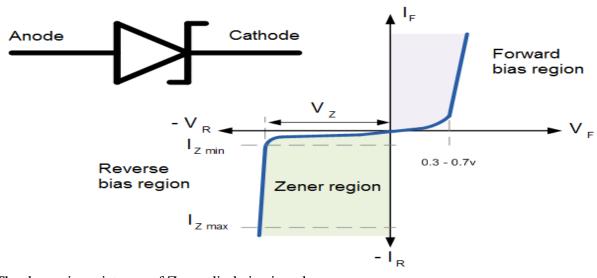

# **ZENER DIODE :**

- The Zener diode is like a general-purpose signal diode consisting of a silicon PN junction.

- When biased in the forward direction it behaves just like a normal signal diode passing the rated current, but as soon as a reverse voltage applied across the zener diode exceeds the rated voltage of the device, the diodes breakdown voltage VB is reached at which point a process called *Avalanche Breakdown occurs in the* semiconductor depletion layer and a current starts to flow through the diode to limit this increase in voltage.

- The current now flowing through the zener diode increases dramatically to the maximum circuit value (which is usually limited by a series resistor) and once achieved this reverse saturation current remains fairly constant over a wide range of applied voltages. This breakdown voltage point, VB is called the "zener voltage" for zener diodes and can range from less than one volt to hundreds of volts.

#### Symbol and V-I Characteristics:

The dynamic resistance of Zener diode is given by

$r_z = \Delta V z / \Delta I z$

- The point at which the zener voltage triggers the current to flow through the diode can be very accurately controlled (to less than 1% tolerance) in the doping stage of the diodes semiconductor construction giving the diode a specific *zener breakdown voltage*, (*Vz*) for *example*, 4.3V or 7.5V.

- *This* zener breakdown voltage on the I-V curve is almost a vertical straight line.

- The Zener Diode is used in its "reverse bias" or reverse breakdown mode, i.e. the diodes anode connects to the negative supply.

- From the I-V characteristics curve above, we can see that the zener diode has a region in its reverse bias characteristics of almost a constant negative voltage regardless of the value of the current flowing through the diode and remains nearly constant even with large changes in current as long as the zener diodes current remains between the breakdown current IZ(min) and the maximum current rating IZ(max).

- This ability to control itself can be used to great effect to regulate or stabilize a voltage source against supply or load variations. The fact that the voltage across the diode in the breakdown region is almost constant turns out to be an important application of the zener diode as a voltage regulator.

The function of a regulator is to provide a constant output voltage to a load connected in parallel with it in spite of the ripples in the supply voltage or the variation in the load current and the zener diode will continue to regulate the voltage until the diodes current falls below the minimum IZ(min) value in the reverse breakdown region. Applications:

- Zener diodes are used in Voltage stabilizers (or) shunt regulators

- used in Surge suppression circuitry for device protection

- used in Over voltage protection circuits.

- Zener diodes are used in clipping and clamping circuits especially peak clippers .

- They are used as Reference elements.

- Used in switching applications.

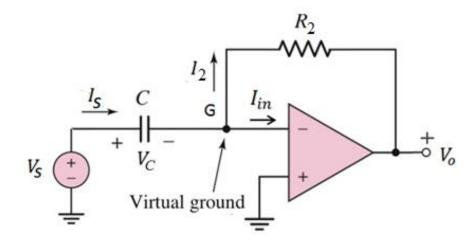

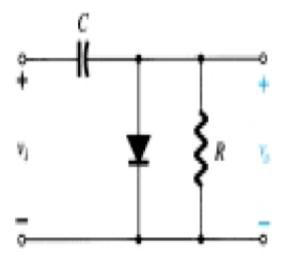

# **Clamper Circuits:**

- A Clamper Circuit is a circuit that adds a DC level to an AC signal. Actually, the positive and negative peaks of the signals can be placed at desired levels using the clamping circuits. As the DC level gets shifted, a clamper circuit is called as a **Level Shifter**.

- Clamper circuits consist of energy storage elements like capacitors. A simple clamper circuit comprises of a capacitor, a diode, a resistor and a dc battery if required.

- A Clamper circuit can be defined as the circuit that consists of a diode, a resistor and a capacitor that shifts the waveform to a desired DC level without changing the actual appearance of the applied signal.

- A Clamper circuit can be defined as the circuit that consists of a diode, a resistor and a capacitor that shifts the waveform to a desired DC level without changing the actual appearance of the applied signal.

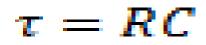

- In order to maintain the time period of the wave form, the  $\tau$  must be greater than, half the time period discharging time of the capacitor should be slow.

### Where

- R is the resistance of the resistor employed

- C is the capacitance of the capacitor used

- The time constant of charge and discharge of the capacitor determines the output of a clamper circuit.

- In a clamper circuit, a vertical shift of upward or downward takes place in the output waveform with respect to the input signal.

- The load resistor and the capacitor affect the waveform. So, the discharging time of the capacitor should be large enough.

- The DC component present in the input is rejected when a capacitor coupled network is used as a capacitor blocks dc. Hence when **dc** needs to be **restored**, clamping circuit is used.

# **Types of Clampers:**

There are few types of clamper circuits, such as

- Positive Clamper

- ✤ Positive clamper with positive V<sub>r</sub>

- ✤ Positive clamper with negativeVr

- Negative Clamper

- ✤ Negative clamper with positive V<sub>r</sub>

- ✤ Negative clamper with negative V<sub>r</sub>

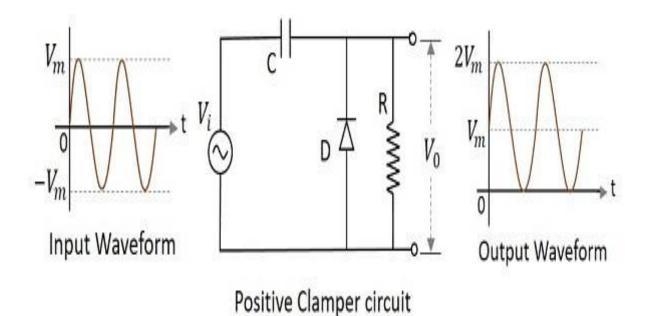

# **Positive Clamper Circuit:**

- A Clamping circuit restores the DC level. When a negative peak of the signal is raised above to the zero level, then the signal is said to be **positively clamped**.

- A Positive Clamper circuit is one that consists of a diode, a resistor and a capacitor and that shifts the output signal to the positive portion of the input signal.

Initially when the input is given, the capacitor is not yet charged and the diode is reverse biased. The output is not considered at this point of time.

- During the negative half cycle, at the peak value, the capacitor gets charged with negative on one plate and positive on the other. The capacitor is now charged to its peak value V<sub>m</sub> The diode is forward biased and conducts heavily.

- During the next positive half cycle, the capacitor is charged to positive V<sub>m</sub> while the diode gets reverse biased and gets open circuited.

- The output of the circuit at this moment will be

V<sub>o</sub>=V<sub>i</sub>+Vm

• The output signal changes according to the changes in the input, but shifts the level according to the charge on the capacitor, as it adds the input voltage.

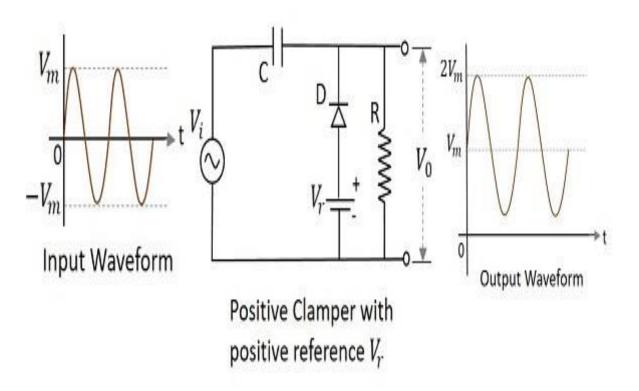

# Positive Clamper with Positive Vr

- A Positive clamper circuit if biased with some positive reference voltage, that voltage will be added to the output to raise the clamped level.

- During the positive half cycle, the reference voltage is applied through the diode at the output and as the input voltage increases, the cathode voltage of the diode increase with respect to the anode voltage and hence it stops conducting.

- During the negative half cycle, the diode gets forward biased and starts conducting. The voltage across the capacitor and the reference voltage together maintain the output voltage level.

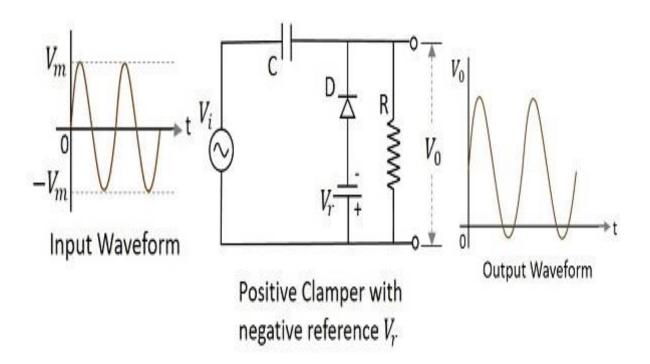

#### **Positive Clamper with Negative Vr:**

- A Positive clamper circuit if biased with some negative reference voltage, that voltage will be added to the output to raise the clamped level

- During the positive half cycle, the voltage across the capacitor and the reference voltage together maintain the output voltage level.

- During the negative half-cycle, the diode conducts when the cathode voltage gets less than the anode voltage.

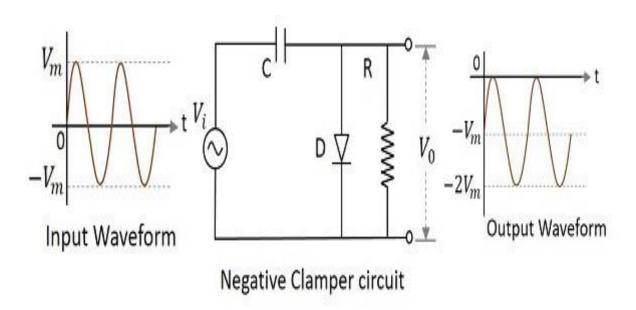

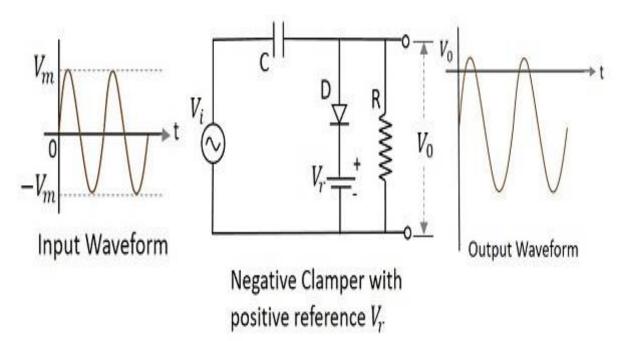

#### **Negative Clamper:**

٠

• A Negative Clamper circuit is one that consists of a diode, a resistor and a capacitor and that shifts the output signal to the negative portion of the input signal.

During the positive half cycle, the capacitor gets charged to its peak value  $V_m$ . The diode is forward biased and conducts.

• During the negative half cycle, the diode gets reverse biased and gets open circuited. The output of the circuit at this moment will be

$$V_0 = V_i + V_m$$

• Hence the signal is negatively clamped as shown in the above figure. The output signal changes according to the changes in the input, but shifts the level according to the charge on the capacitor, as it adds the input voltage.

#### Negative clamper with positive Vr

- A Negative clamper circuit if biased with some positive reference voltage, that voltage will be added to the output to raise the clamped level. Though the output voltage is negatively clamped, a portion of the output waveform is raised to the positive level, as the applied reference voltage is positive.

- During the positive half-cycle, the diode conducts, but the output equals the positive reference voltage applied.

- During the negative half cycle, the diode acts as open circuited and the voltage across the capacitor forms the output.

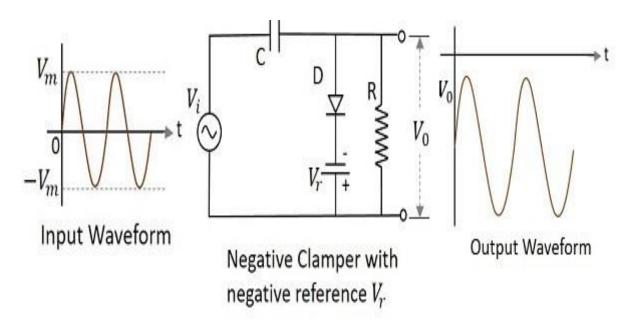

#### Negative Clamper with Negative V<sub>r</sub>

- A Negative clamper circuit if biased with some negative reference voltage, that voltage will be added to the output to raise the clamped level.

- The cathode of the diode is connected with a negative reference voltage, which is less than that of zero and the anode voltage. Hence the diode starts conducting during positive half cycle, before the zero voltage level.

During the negative half cycle, the voltage across the capacitor appears at the output. Thus the waveform is clamped towards the negative portion.

#### **Applications:**

- Used as direct current restorers

- Used to remove distortions

- Used as voltage multipliers

- Used for the protection of amplifiers

- Used as test equipment

- Used as base-line stabilizer

#### **CLIPPING CIRCUITS:**

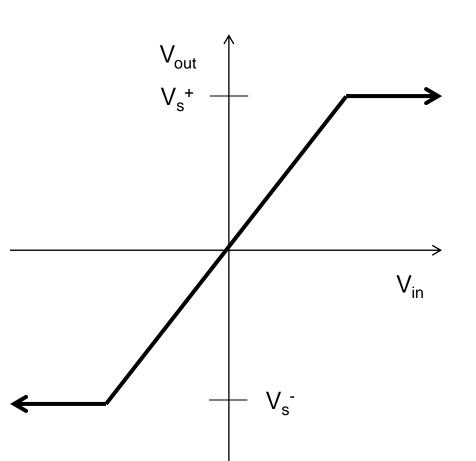

- A Clipper circuit is a circuit that rejects the part of the input wave specified while allowing the remaining portion. The portion of the wave above or below the cut off voltage determined is clipped off or cut off.

- The clipping circuits consist of linear and non-linear elements like resistors and diodes but not energy storage elements like capacitors.

#### **ADVANTAGES:**

- To eliminate the unwanted noise present in the amplitudes.

- These can work as square wave converters, as they can convert sine waves into square waves by clipping.

- The amplitude of the desired wave can be maintained at a constant level.

#### **TYPES:**

Diode Clippers are two main types

#### 1. Positive clippers and

#### 2. Negative clippers

**Positive clippers:** The Clipper circuit that is intended to attenuate positive portions of the input signal

Among the positive diode clipper circuits, we have the following types -

- Positive Series Clipper

- Positive Series Clipper with positive V<sub>r</sub>

- Positive Series Clipper with negative V<sub>r</sub>

- Positive Shunt Clipper

- Positive Shunt Clipper with positive V<sub>r</sub>

- Positive Shunt Clipper with negative V<sub>r</sub>

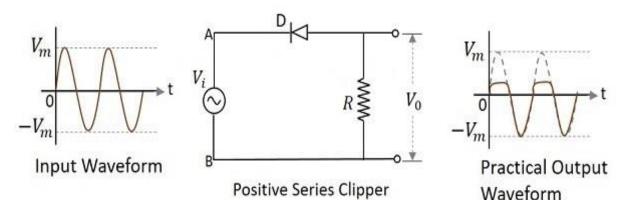

#### **POSITIVE SERIES CLIPPER**

• A Clipper circuit in which the diode is connected in series to the input signal and that attenuates the positive portions of the waveform, is termed as **Positive Series Clipper**

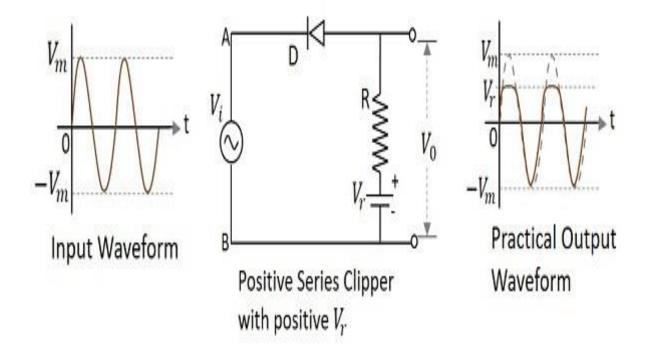

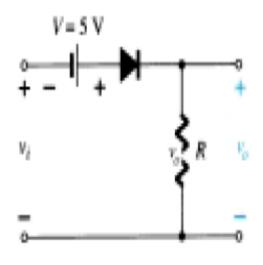

#### **Positive Series Clipper with positive** V<sub>r</sub>

- A Clipper circuit in which the diode is connected in series to the input signal and biased with positive reference voltage  $V_r$  and that attenuates the positive portions of the waveform, is termed as **Positive Series Clipper with positive**  $V_r$

- During the positive cycle of the input the diode gets reverse biased and the reference voltage appears at the output.

• During its negative cycle, the diode gets forward biased and conducts like a closed switch.

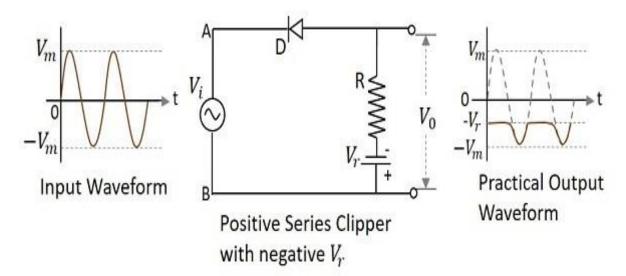

#### Positive Series Clipper with negative $\mathbf{V}_{\mathbf{r}}$

- A Clipper circuit in which the diode is connected in series to the input signal and biased with negative reference voltage V<sub>r</sub> and that attenuates the positive portions of the waveform, is termed as **Positive Series Clipper with negative** V<sub>r</sub>

- During the positive cycle of the input the diode gets reverse biased and the reference voltage appears at the output. As the reference voltage is negative, the same voltage with constant amplitude is shown.

- During its negative cycle, the diode gets forward biased and conducts like a closed switch. Hence the input signal that is greater than the reference voltage, appears at the output.

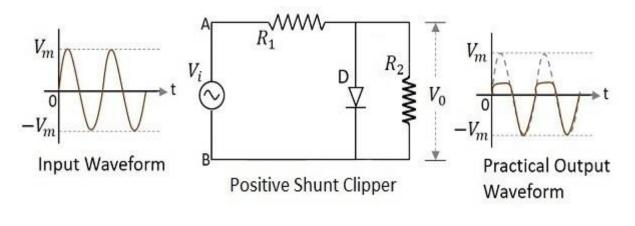

#### **Positive Shunt Clipper**

• A Clipper circuit in which the diode is connected in shunt to the input signal and that attenuates the positive portions of the waveform, is termed as **Positive Shunt Clipper**.

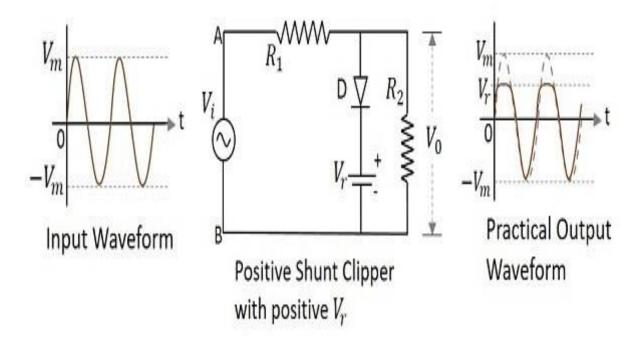

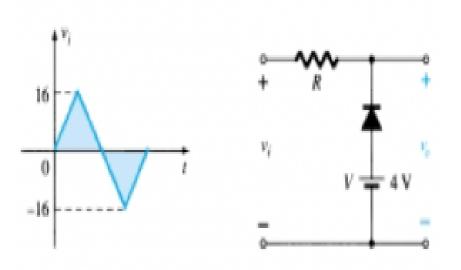

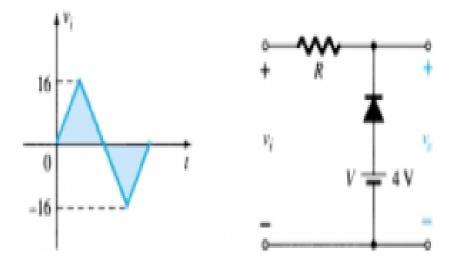

#### Positive Shunt Clipper with positive V<sub>r</sub>

- A Clipper circuit in which the diode is connected in shunt to the input signal and biased with positive reference voltage V<sub>r</sub> and that attenuates the positive portions of the waveform, is termed as **Positive Shunt Clipper with positive** V<sub>r</sub>

- During the positive cycle of the input the diode gets forward biased and nothing but the reference voltage appears at the output.

- During its negative cycle, the diode gets reverse biased and behaves as an open switch. The whole of the input appears at the output.

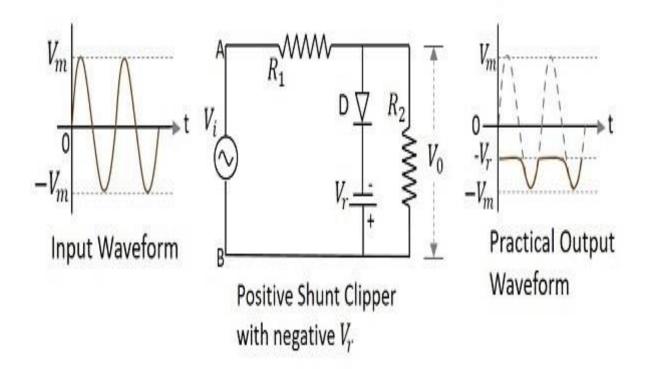

#### Positive Shunt Clipper with negative Vr

- A Clipper circuit in which the diode is connected in shunt to the input signal and biased with negative reference voltage V<sub>r</sub> and that attenuates the positive portions of the waveform, is termed as **Positive Shunt Clipper with negative** V<sub>r</sub>

- During the positive cycle of the input, the diode gets forward biased and the reference voltage appears at the output. As the reference voltage is negative, the same voltage with constant amplitude is shown.

- During its negative cycle, the diode gets reverse biased and behaves as an open switch. Hence the input signal that is greater than the reference voltage, appears at the output.

#### **Negative Clipper:**

• The Clipper circuit that is intended to attenuate negative portions of the input signal can be termed as a **Negative Clipper**.

Among the negative diode clipper circuits, we have the following types.

• Negative Series Clipper

Negative Series Clipper with positive V<sub>r</sub> Negative Series Clipper with negative V<sub>r</sub>

• Negative Shunt Clipper

Negative Shunt Clipper with positive  $V_r$ Negative Shunt Clipper with negative  $V_r$

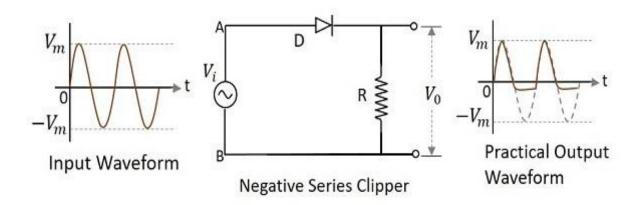

#### **Negative Series Clipper**

• A Clipper circuit in which the diode is connected in series to the input signal and that attenuates the negative portions of the waveform, is termed as **Negative Series Clipper**.

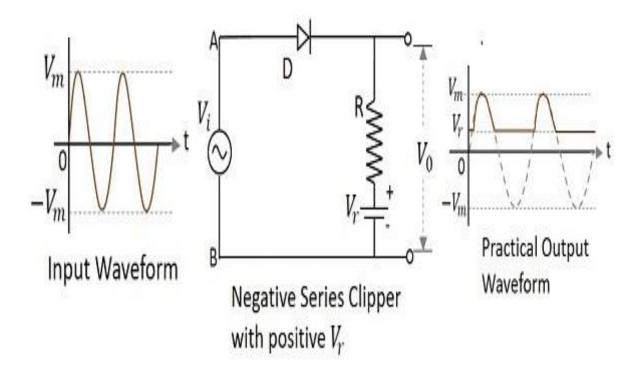

#### Negative Series Clipper with positive Vr

- A Clipper circuit in which the diode is connected in series to the input signal and biased with positive reference voltage  $V_r$  and that attenuates the negative portions of the waveform, is termed as **Negative Series Clipper with positive**  $V_r$

- During the positive cycle of the input, the diode starts conducting only when the anode voltage value exceeds the cathode voltage value of the diode. As the cathode voltage equals the reference voltage applied, the output will be as shown.

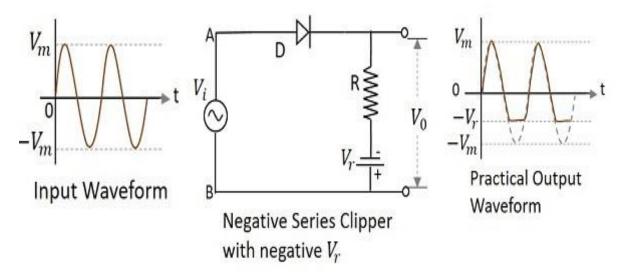

#### Negative Series Clipper with negative Vr

- A Clipper circuit in which the diode is connected in series to the input signal and biased with negative reference voltage  $V_r$  and that attenuates the negative portions of the waveform, is termed as **Negative Series Clipper with negative**  $V_r$

- During the positive cycle of the input the diode gets forward biased and the input signal appears at the output.

- During its negative cycle, the diode gets reverse biased and hence will not conduct. But the negative reference voltage being applied, appears at the output. Hence the negative cycle of the output waveform gets clipped after this reference level.

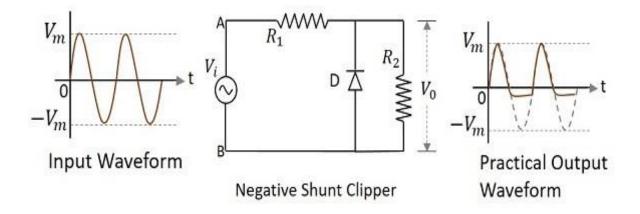

#### **Negative Shunt Clipper:**

• A Clipper circuit in which the diode is connected in shunt to the input signal and that attenuates the negative portions of the waveform, is termed as Negative Shunt Clipper.

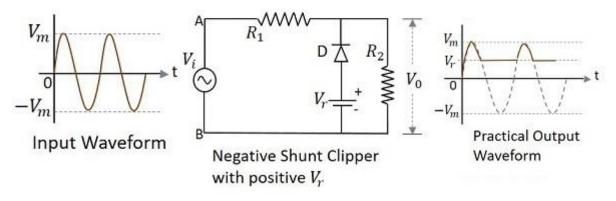

#### Negative Shunt Clipper with positive Vr

- A Clipper circuit in which the diode is connected in shunt to the input signal and biased with positive reference voltage V<sub>r</sub> and that attenuates the negative portions of the waveform, is termed as Negative Shunt Clipper with positive V<sub>r</sub>

- During the positive cycle of the input the diode gets reverse biased and behaves as an open switch. So whole of the input voltage, which is greater than the reference voltage applied, appears at the output. The signal below reference voltage level gets clipped off. During the negative half cycle, as the diode gets forward biased and the loop gets completed, no output is present.

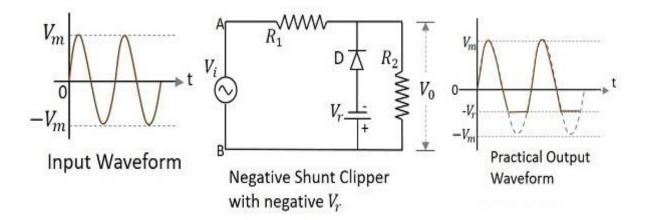

#### Negative Shunt Clipper with negative Vr

- A Clipper circuit in which the diode is connected in shunt to the input signal and biased with negative reference voltage Vr and that attenuates the negative portions of the waveform, is termed as Negative Shunt Clipper with negative Vr

- During the positive cycle of the input the diode gets reverse biased and behaves as an open switch. So whole of the input voltage, appears at the output  $V_o$

- During the negative half cycle, the diode gets forward biased. The negative voltage up to the reference voltage, gets at the output and the remaining signal gets clipped off.

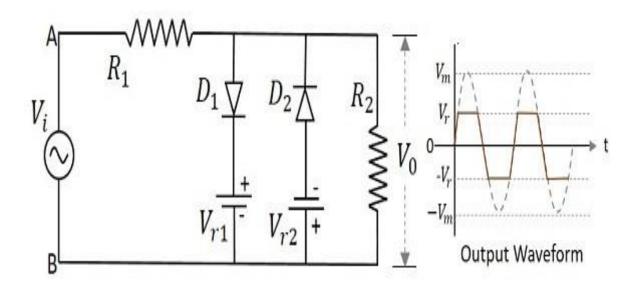

#### **Two-way Clipper:**

- This is a positive and negative clipper with a reference voltage  $V_r$ . The input voltage is clipped two-way both positive and negative portions of the input waveform with two reference voltages. For this, two diodes  $D_1$  and  $D_2$  along with two reference voltages  $V_{r1}$  and  $V_{r2}$  are connected in the circuit.

- This circuit is also called as a Combinational Clipper circuit.

During the positive half of the input signal, the diode  $D_1$  conducts making the reference voltage  $V_{r1}$  appear at the output. During the negative half of the input signal, the diode  $D_2$  conducts making the reference voltage  $V_{r2}$  appear at the output. Hence both the diodes conduct alternatively to clip the output during both the cycles. The output is taken across the load resistor.

Applications:

- Used for the generation and shaping of waveforms

- Used for the protection of circuits from spikes

- Used for amplitude restorers

- Used as voltage limiters

- Used in television circuits

- Used in FM transmitters

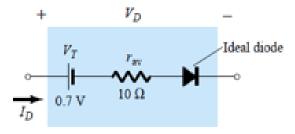

#### MODELING AND ANALYSIS OF DIODE:

#### **Equivalent Circuit:**

- An Equivalent circuit is a combination of elements properly chosen to best represent the actual characteristics of device in a particular operating region.

- Need of Equivalent circuit:

- To find the Parameters like current, voltage using circuit analysis methods.

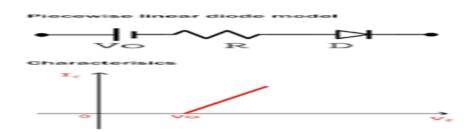

#### Models:

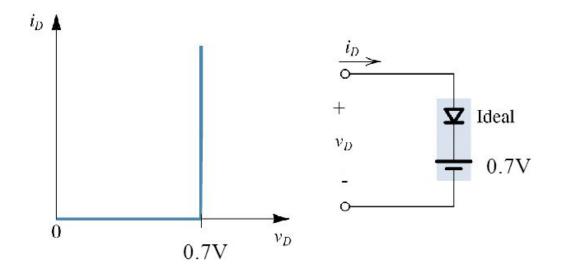

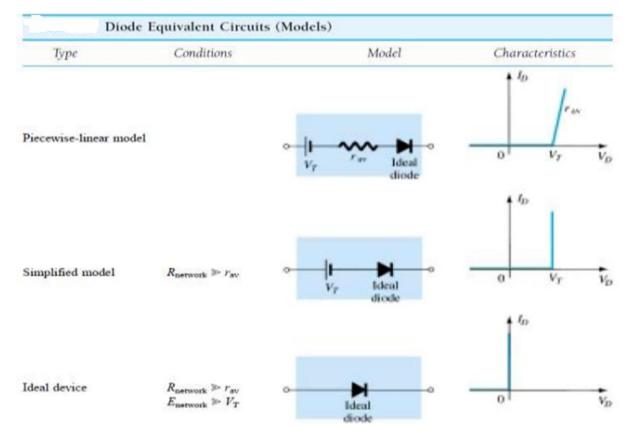

- Piecewise linear model

- Assumptions : Linear even with small non linearity

- Constant voltage drop model

- Ideal diode model

Piecewise linear model:

The real diode is modelled as 3 components in series: an ideal diode, a voltage source and a <u>resistor</u>

Ideal Diode Model:

- a) The voltage across the diode is zero for forward bias.

- b) The slope of the current voltage curve is infinite for forward bias.

- c) The current across the diode is zero for reverse bias.

Constant Voltage Drop (CVD) Model:

- a) The voltage across the diode is a non-zero value for forward bias. Normally this is taken as 0.6 or 0.7 volts.

- b) The slope of the current voltage curve is infinite for forward bias.

c) The current across the diode is zero for reverse bias.

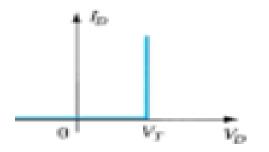

I-V characteristics and equivalent circuit

#### **TUTORIAL PROBLEMS:**

- 1. The depletion region or space charge region or transition region in a semiconductor p-n junction diode has

- a) electrons and holes.

- b) positive ions and electrons.

- c) positive and negative ions.

- d) negative ions and holes

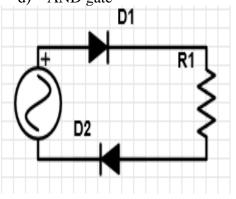

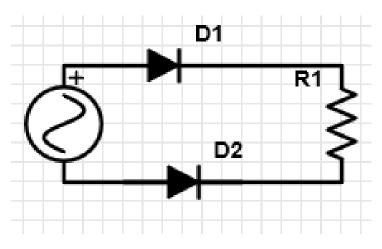

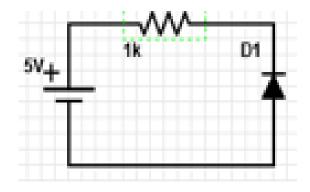

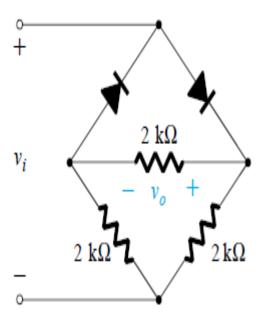

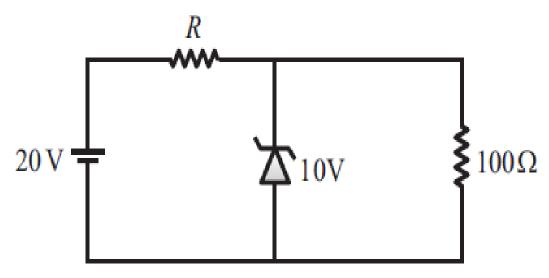

- 2. Which circuit has been represented in the associated circuit diagram?

- a) Half wave rectifier

- b) Full wave rectifier

- c) NOT gate

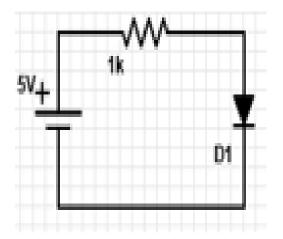

3. Which circuit has been represented in the associated circuit diagram?

- a) Half wave rectifier

- b) Full wave rectifier

- c) NOT gate

- d) AND gate

4. Which of the following is not a valid form of a diode equivalent circuit?a) Piecewise Linear Model

- b) Ideal Diode Modelc) Simplified Modeld) Differential Model

- 5. From the given I-V characteristics of a silicon diode, what is the approximate value of  $r_{av}$  between marked points?

- a) 7 ohms

- b) 11.2 ohms

- c) 8 ohms

- d) 6 ohms

6. Assuming the diode in the given circuit diagram to be a silicon p-n junction diode, what is the current for the given circuit diagram?

- a) 4.3 mA

- b) 0

- c) 43 mA

- d) 5 mA

- 7. Assuming the diode in the given circuit diagram to be a silicon p-n junction diode, what is the current for the given circuit diagram?

- a) 0

- b) 5 mA

- c) 4.3 mA

- d) Can't be determined

- 8. Which of the following equations is correct for a full wave rectified output?

- a)  $\left|V_{dc}\right|=0.318~V_{p}$

- b)  $|V_{dc}| = 0.636 V_p$

- c)  $|V_{dc}| = 0.477 V_p$

- d)  $|V_{dc}| = 0.211 V_p$

- 9. Which of the following statements are true about the given circuit?

a) The circuit is that of a bridge rectifier

b) The PIV of the diode D1 must be greater than v0 for the circuit to function as a bridge rectifier

c) For silicon diodes, the value of  $v_0=(v_i-1.4)$  V

d) All of the mentioned

- 10. In the given circuit, what will be the nature of the output waveform?a) Half rectifiedb) Full rectifiedc) Sinusoidal

- d)DC

# **MODULE II BJT AND** AMPLIFIER CIRCUITS

# Transistor

- A **Transistor** is a three terminal semiconductor device that regulates current or voltage flow and acts as a switch or gate for signals.

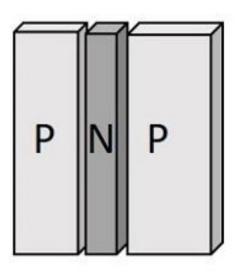

- If a P-type material or N-type material is added to a single PN junction, another junction will be formed. Such a formation is simply called as a **Transistor**.

# **Constructional Details of a Transistor**

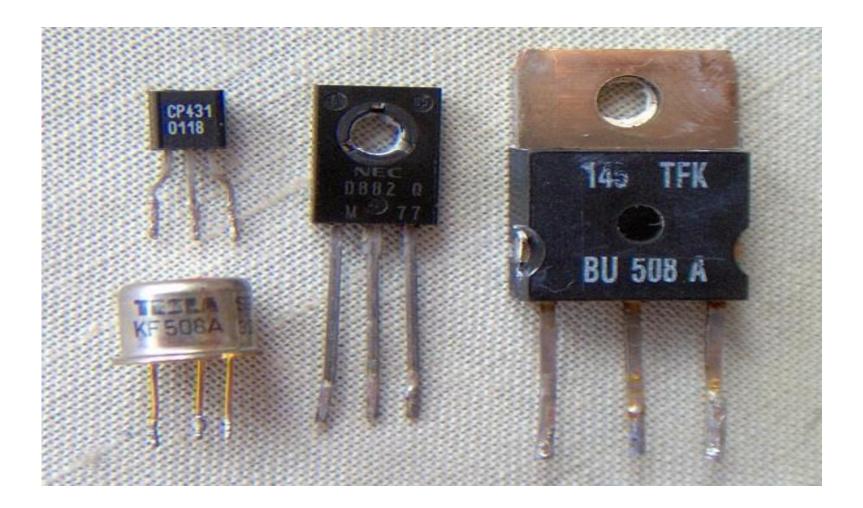

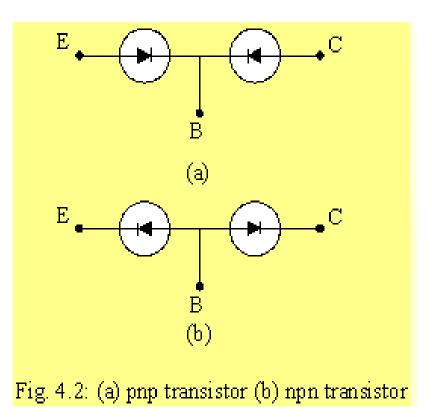

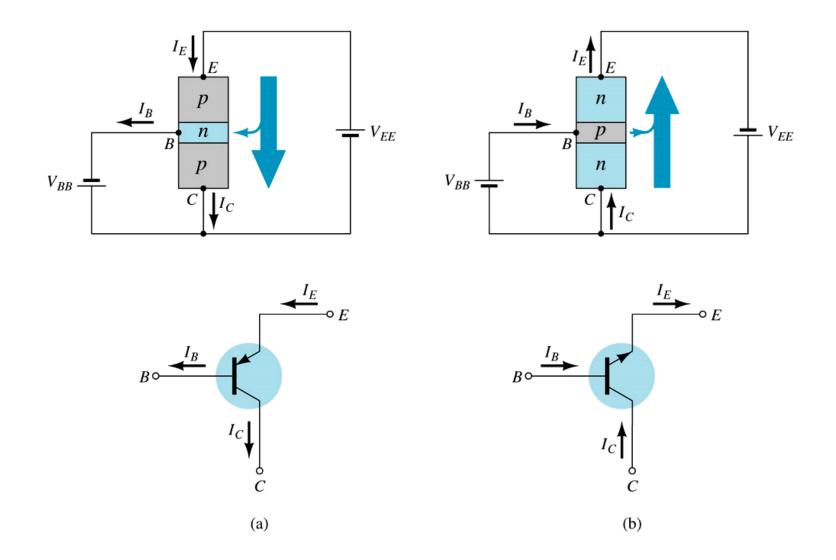

The Transistor is a three terminal solid state device which is formed by connecting two diodes back to back. Hence it has got two PN junctions. Three terminals are drawn out of the three semiconductor materials present in it. This type of connection offers two types of transistors. They are PNP and NPN which means an N-type material between two Ptypes and the other is a P-type material between two N-types respectively.

# **Constructional Details of a Transistor**

The three terminals drawn from the transistor indicate **Emitter, Base** and **Collector** terminals.

# Emitter

- The left-hand side of the above shown structure can be understood as **Emitter**.

- This has a moderate size and is heavily doped as its main function is to supply a number of majority carriers, i.e. either electrons or holes.

- As this emits electrons, it is called as an Emitter.

- This is simply indicated with the letter **E**.

## Base

- The middle material in the above figure is the **Base**.

- This is **thin** and **lightly doped**.

- Its main function is to **pass** the majority carriers from the emitter to the collector.

- This is indicated by the letter **B**.

# Collector

- The right side material in the above figure can be understood as a **Collector**.

- Its name implies its function of collecting the carriers.

- This is a **bit larger** in size than emitter and base. It is **moderately doped**.

- This is indicated by the letter **C**

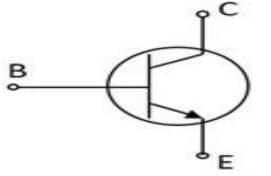

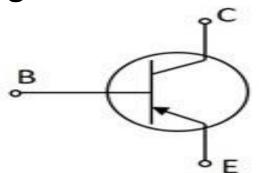

# Symbol

The **arrow-head** in the figures indicated the **emitter** of a transistor. As the collector of a transistor has to dissipate much greater power, it is made large. Due to the specific functions of emitter and collector, they are **not interchangeable**. Hence the terminals are always

to be kept in mind while using a transistor.

NPN transistor

# Transistor

# Position of the terminals and symbol of BJT.

- Base is located at the middle and more thin from the level of collector and emitter

- The emitter and collector terminals are made of the same type of semiconductor material, while the base of the other type of material

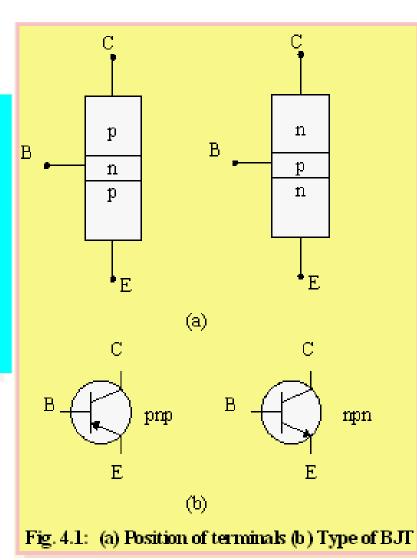

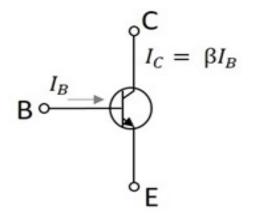

### Transistor currents

$I_{C}$ =the collector current  $I_{B}$ = the base current  $I_{E}$ = the emitter current -The arrow is always drawn on the emitter

-The arrow always point toward the n-type

-The arrow indicates the direction of the emitter current:

pnp: $E \rightarrow B$ npn:  $B \rightarrow E$

- By imaging the analogy of diode, transistor can be construct like two diodes that connetecd together.

- It can be conclude that the work of transistor is base on work of diode.

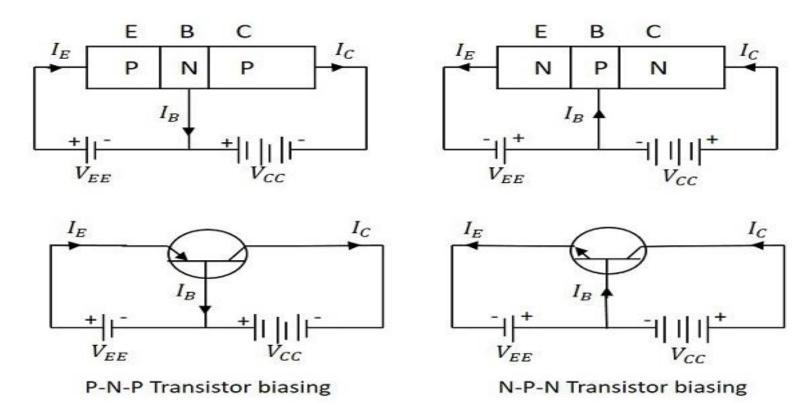

# **Transistor Biasing**

- Biasing is controlling the operation of the circuit by providing power supply. The function of both the PN junctions is controlled by providing bias to the circuit through some dc supply.

- we have two junctions here. As one junction is between the emitter and base, that is called as Emitter-Base junction and likewise, the other is Collector-Base junction.

# **Transistor Biasing**

- The N-type material is provided negative supply and Ptype material is given positive supply to make the circuit Forward bias.

- The N-type material is provided positive supply and Ptype material is given negative supply to make the circuit **Reverse bias**.

- By applying the power, the emitter base junction is always forward biased as the emitter resistance is very small. The collector base junction is reverse biased and its resistance is a bit higher. A small forward bias is sufficient at the emitter junction whereas a high reverse bias has to be applied at the collector junction.

# **Transistor Biasing**

The direction of current indicated in the circuits above, also called as the **Conventional Current**, is the movement of hole current which is **opposite to the electron current**.

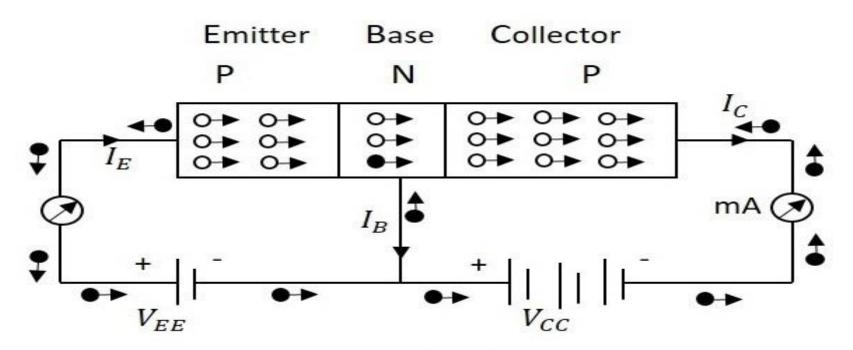

# **Operation of PNP Transistor**

- The voltage  $V_{EE}$  provides a positive potential at the emitter which repels the holes in the P-type material and these holes cross the emitter-base junction, to reach the base region. There a very low percent of holes re-combine with free electrons of N-region. This provides very low current which constitutes the base current  $I_B$ . The remaining holes cross the collector-base junction, to constitute collector current  $I_c$ , which is the hole current.

- As a hole reaches the collector terminal, an electron from the battery negative terminal fills the space in the collector. This flow slowly increases and the electron minority current flows through the emitter, where each electron entering the positive terminal of  $V_{EE}$ , is replaced by a hole by moving towards the emitter junction. This constitutes emitter current  $I_{E}$ .

# **Operation of PNP Transistor**

The conduction in a PNP transistor takes place through holes. The collector current is slightly less than the emitter current. The increase or decrease in the emitter current affects the collector current.

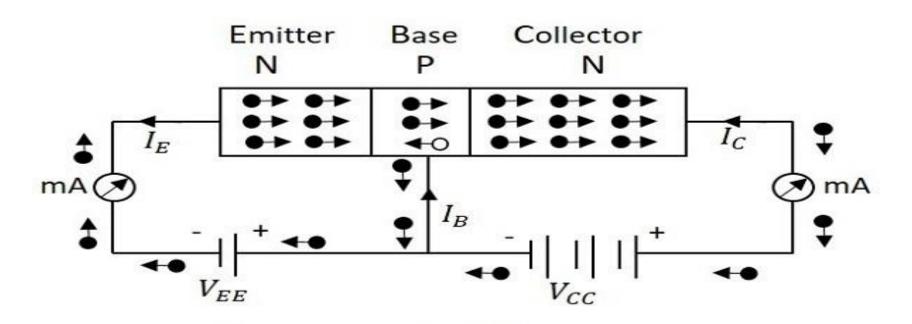

## **Operation of NPN Transistor**

- The voltage  $V_{EE}$  provides a negative potential at the emitter which repels the electrons in the N-type material and these electrons cross the emitter-base junction, to reach the base region. There, a very low percent of electrons re-combine with free holes of P-region. This provides very low current which constitutes the base current  $I_B$ . The remaining holes cross the collector-base junction, to constitute the collector current  $I_C$ .

- As an electron reaches out of the collector terminal, and enters the positive terminal of the battery, an electron from the negative terminal of the battery  $V_{EE}$  enters the emitter region. This flow slowly increases and the electron current flows through the transistor.

# **Operation of NPN Transistor**

The conduction in a NPN transistor takes place through electrons.

The collector current is higher than the emitter current. The increase or decrease in the emitter current affects the collector current.

# TRANSISTOR CURRENT COMPONENTS

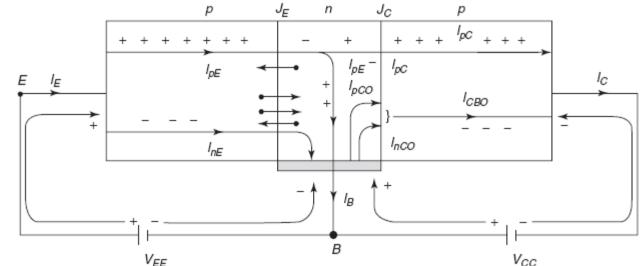

### Current Components in p-n-p Transistor

> Both biasing potentials have been applied to a p-n-p transistor, with the resulting majority and minority carrier flow indicated.

> The width of the depletion region clearly indicates which junction is forwardbiased and which is reverse-biased.

> The magnitude of the base current is typically in the order of microamperes as compared to mill amperes for the emitter and collector currents. The large number of these majority carriers will diffuse across the reverse-biased junction into the *p*-type material connected to the collector terminal

Direction of flow of current in *p*–*n*–*p* transistor with the base–emitter junction forward-biased and the collector–base junction reverse-biased

## TRANSISTOR CURRENT COMPONENTS

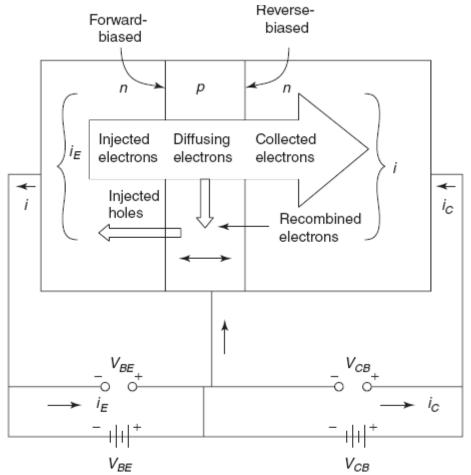

#### **Current Components in an** *n*–*p*–*n Transistor*

The operation of an n-p-ntransistor is the same as that of a pn-p transistor, but with the roles played by the electrons and holes interchanged.

> The polarities of the batteries and also the directions of various currents are to be reversed.

➢ Here the majority electrons from the emitter are injected into the base and the majority holes from the base are injected into the emitter region. These two constitute the emitter current.

The majority and the minority carrier current flow in a forward-biased *n*-*p*-*n* transistor

### Advantages

- High voltage gain.

- Lower supply voltage is sufficient.

- Most suitable for low power applications.

- Smaller and lighter in weight.

- Mechanically stronger than vacuum tubes.

- No external heating required like vacuum tubes.

- Very suitable to integrate with resistors and diodes to produce ICs.

# Disadvantages

- They cannot be used for high power applications due to lower power dissipation.

- They have lower input impedance and they are temperature dependent.

## **Transistor Configurations**

- Any transistor has three terminals, the **emitter**, the **base**, and the **collector**. Using these 3 terminals the transistor can be connected in a circuit with one terminal common to both input and output in three different possible configurations.

- The three types of configurations are Common Base, Common Emitter and Common Collector configurations. In every configuration, the emitter junction is forward biased and the collector junction is reverse biased.

## **CB, CE AND CC CONFIGURATIONS**

Depending on the common terminal between the input and the output circuits of a transistor, it may be operated in the common-base mode, or the common-emitter mode, or the common-collector mode.

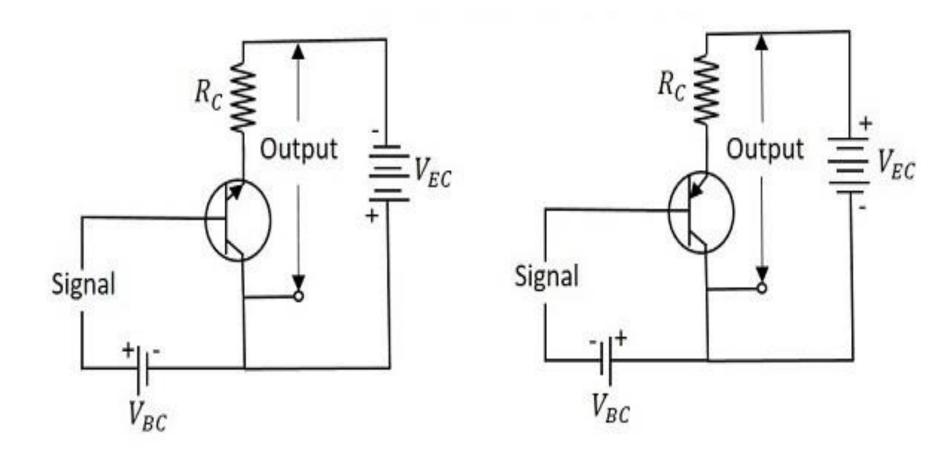

### Common-base (CB) Mode

➤ In this mode, the base terminal is common to both the input and the output circuits. This mode is also referred to as the ground-base configuration.

## **CB, CE AND CC CONFIGURATIONS**

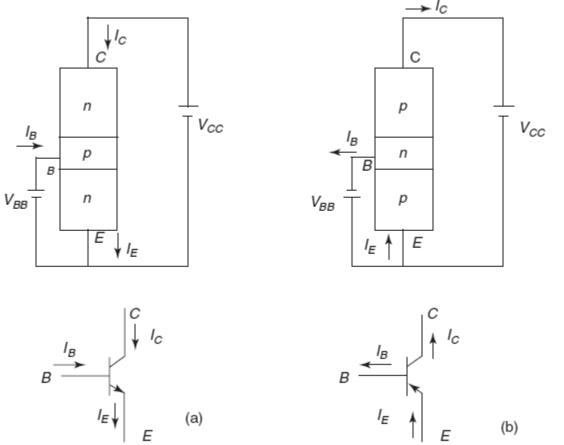

### Common-emitter (CE) Mode

> When the emitter terminal is common to both the input and the output circuits, the mode of operation is called the common-emitter (CE) mode or the ground–emitter configuration of the transistor.

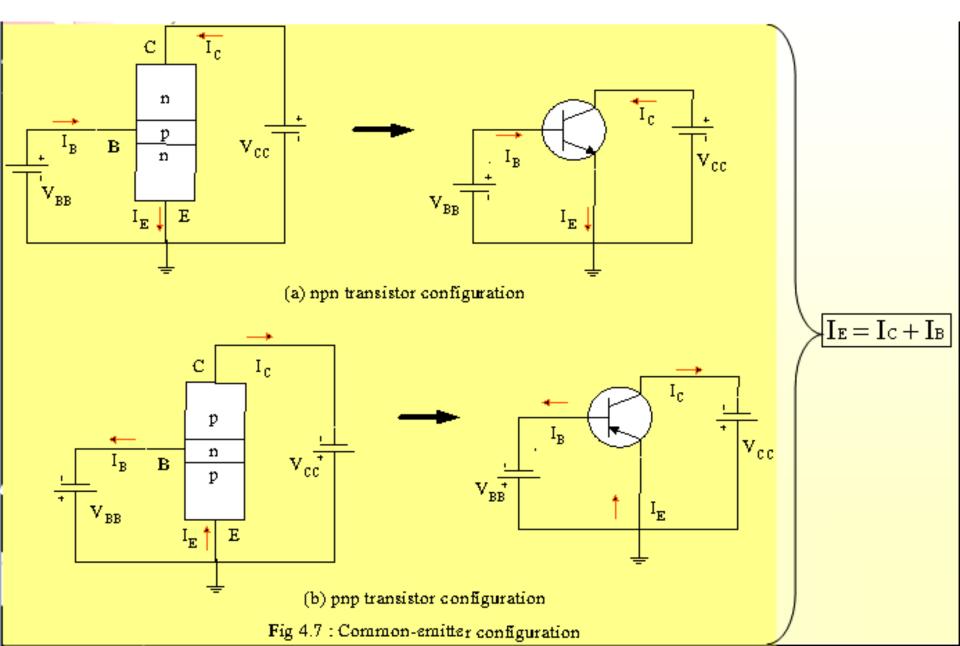

Notation and symbols for common-emitter configuration (a) n-p-n transistor (b) p-n-p transistor

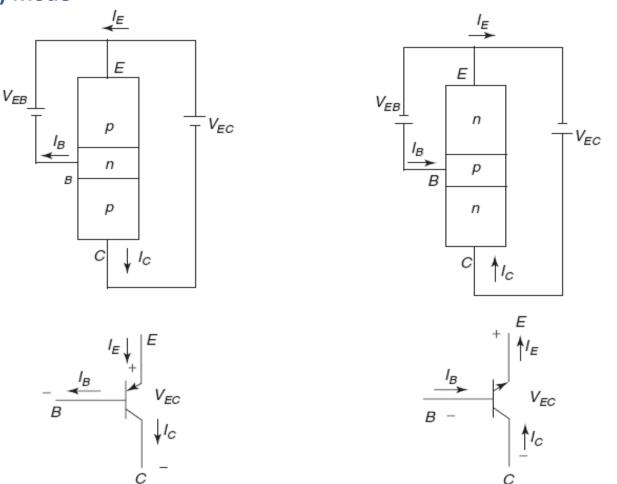

### **CB, CE AND CC CONFIGURATIONS**

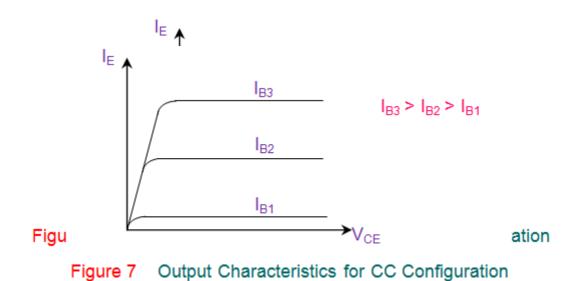

#### Common-collector (CC) Mode

When the collector of terminal the transistor is common to both the input and the output terminals, the mode of operation is known the commonas collector (CC) mode the groundor collector configuration.

**Common-collector configuration**

## **Transistor Characteristics**

- Input Characteristics: These describe the changes in input current with the variation in the values of input voltage keeping the output voltage constant.

- **Output Characteristics**: This is a plot of output current versus output voltage with constant input current.

- **Current Transfer Characteristics**: This characteristic curve shows the variation of output current in accordance with the input current, keeping output voltage constant.

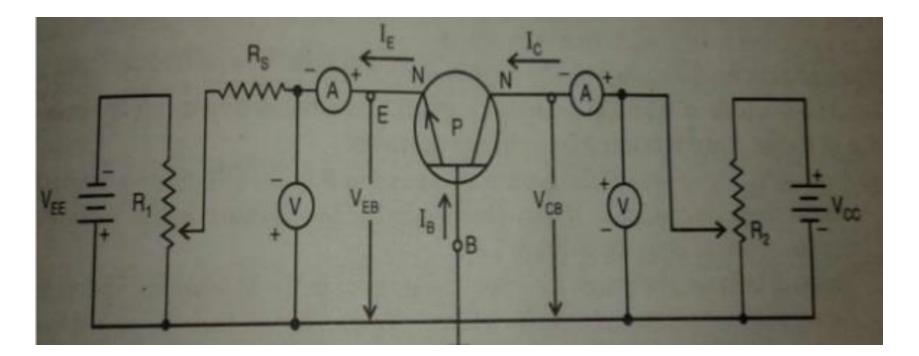

## **Common Base (CB) Configuration**

The name itself implies that the **Base** terminal is taken as common terminal for both input and output of the transistor.

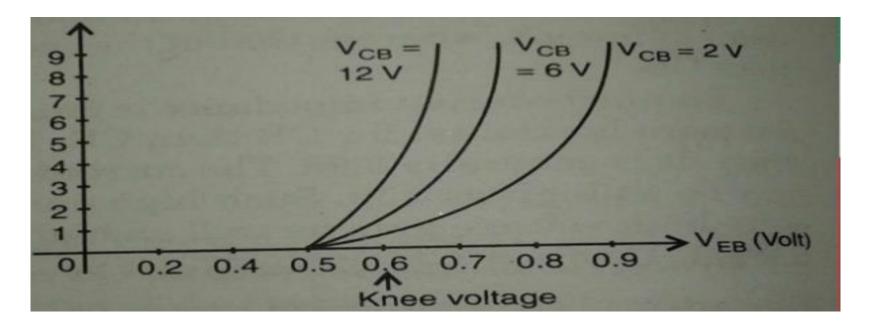

# Input or driving point characteristics.

The input characteristics of a CB configuration circuit which describes the variation of emitter current, I<sub>E</sub> with Base-Emitter voltage, V<sub>BE</sub> keeping Collector-Base voltage, V<sub>CB</sub> constant.

# Input or driving point characteristics.

This leads to the expression for the input resistance as

$$R_{in} = \frac{\Delta V_{BE}}{\Delta I_E} \Big|_{V_{CB} = constant}$$

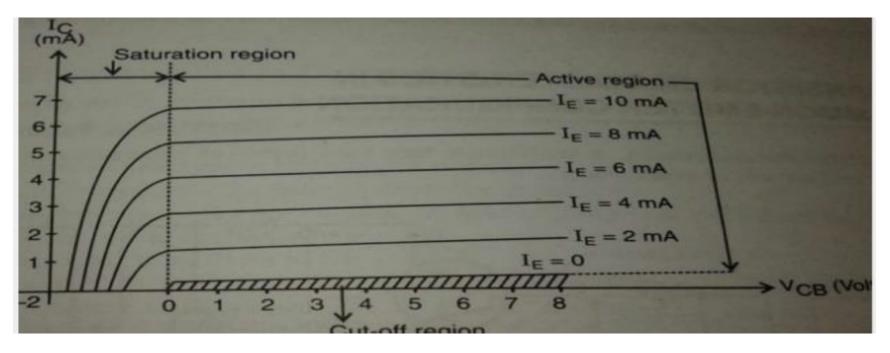

### Output or collector characteristics

The output characteristics of CB configuration (Figure 3) show the variation of collector current,  $I_c$  with  $V_{CB}$  when the emitter current,  $I_E$  is held constant.

# Output or collector characteristics

- The output characteristics has 3 basic regions:

- Active region –defined by the biasing arrangements

- Cutoff region region where the collector current is 0A

- Saturation region- region of the characteristics to the left of  $V_{CB} = 0V$

- From the graph shown, the output resistance can be obtained as:

$$R_{out} = \frac{\Delta V_{CB}}{\Delta I_C} \Big|_{I_E = constant}$$

| Active                                                                                                                                                                                                                                                            | Saturation                                                                                                                                                                                                  | Cut-off                                                                                                                                            |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| region                                                                                                                                                                                                                                                            | region                                                                                                                                                                                                      | region                                                                                                                                             |

| <ul> <li>IE increased, Ic increased</li> <li>BE junction forward bias<br/>and CB junction reverse<br/>bias</li> <li>Refer to the graf, Ic ≈ IE</li> <li>Ic not depends on VcB</li> <li>Suitable region for the<br/>transistor working as<br/>amplifier</li> </ul> | <ul> <li>BE and CB junction<br/>is forward bias</li> <li>Small changes in Vсв<br/>will cause big different<br/>to Ic</li> <li>The allocation for<br/>this region is to the<br/>left of Vсв= 0 V.</li> </ul> | <ul> <li>Region below the line of IE=0 A</li> <li>BE and CB is reverse bias</li> <li>no current flow at collector, only leakage current</li> </ul> |

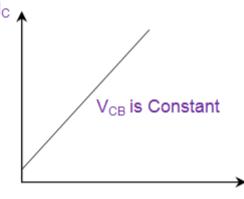

## **Current Transfer Characteristics**

The current transfer characteristics for CB configuration which illustrates the variation of I<sub>C</sub> with the I<sub>E</sub> keeping V<sub>CB</sub> as a constant. The resulting current gain has a value less than 1 and can be mathematically expressed as:

ΊF

## Characteristics of CB configuration

- This configuration provides voltage gain but no current gain.

- Being V<sub>CB</sub> constant, with a small increase in the Emitter-base voltage V<sub>EB</sub>, Emitter current I<sub>E</sub> gets increased.

- Emitter Current I<sub>E</sub> is independent of Collector voltage V<sub>CB</sub>.

- Collector Voltage V<sub>CB</sub> can affect the collector current I<sub>C</sub> only at low voltages, when V<sub>EB</sub> is kept constant.

- The input resistance R<sub>i</sub> is the ratio of change in emitter-base voltage (ΔV<sub>EB</sub>) to the change in emitter current (ΔI<sub>E</sub>) at constant collector base voltage V<sub>CB</sub>.

$$R_i = rac{\Delta V_{EB}}{\Delta I_E}$$

at constant V<sub>CB</sub>

- As the input resistance is of very low value, a small value of V<sub>EB</sub> is enough to produce a large current flow of emitter current I<sub>E</sub>.

- The output resistance R<sub>o</sub> is the ratio of change in the collector base voltage (ΔV<sub>CB</sub>) to the change in collector current (ΔI<sub>C</sub>) at constant emitter current IE.

$$R_o = rac{\Delta V_{CB}}{\Delta I_C}$$

at constant I<sub>E</sub>

# Characteristics of CB configuration

- As the output resistance is of very high value, a large change in V<sub>CB</sub> produces a very little change in collector current I<sub>C</sub>.

- This Configuration provides good stability against increase in temperature.

- The CB configuration is used for high frequency applications.

### Expression for Collector current

With the above idea, let us try to draw some expression for collector current.

Along with the emitter current flowing, there is some amount of base current  $I_B$  which flows through the base terminal due to electron hole recombination. As collector-base junction is reverse biased, there is another current which is flown due to minority charge carriers. This is the leakage current which can be understood as  $I_{leakage}$ . This is due to minority charge carriers carriers and hence very small.

The emitter current that reaches the collector terminal is

### $\alpha I_E$

Total collector current

$I_C = \alpha I_E + I_{leakage}$

If the emitter-base voltage  $V_{EB} = 0$ , even then, there flows a small leakage current, which can be termed as  $I_{CBO}$  (collector-base current with output open).

The collector current therefore can be expressed as

$$egin{aligned} &I_C = lpha I_E + I_{CBO} \ &I_E = I_C + I_B \ &I_C = lpha (I_C + I_B) + I_{CBO} \ &I_C (1-lpha) = lpha I_B + I_{CBO} \ &I_C = rac{lpha}{1-lpha} I_B + rac{I_{CBO}}{1-lpha} \ &I_C = \left(rac{lpha}{1-lpha}

ight) I_B + \left(rac{1}{1-lpha}

ight) I_{CBO} \end{aligned}$$

The value of collector current depends on base current and leakage current along with the current amplification factor of that transistor in use.

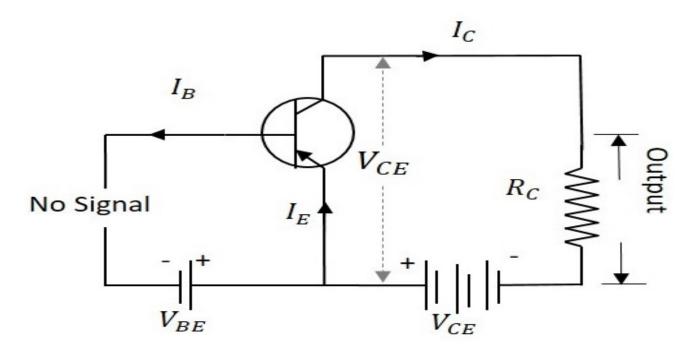

### **Common-Emitter Configuration**

- It is called common-emitter configuration since :

- emitter is common or reference to both input and output terminals.

- emitter is usually the terminal closest to or at ground potential.

- Almost amplifier design is using connection of CE due to the high gain for current and voltage.

- Two set of characteristics are necessary to describe the behavior for CE ;input (base terminal) and output (collector terminal) parameters.

### Proper Biasing common-emitter configuration in active region

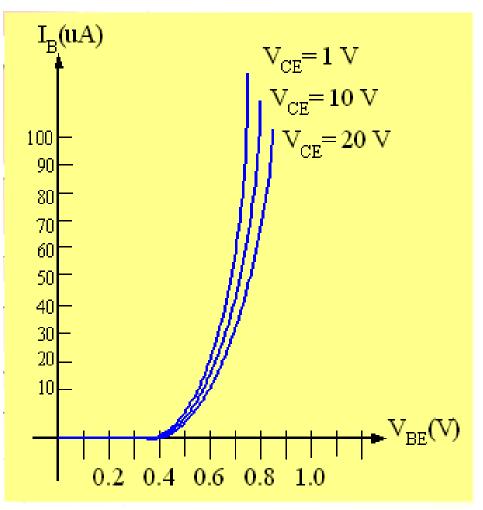

# Input characteristics

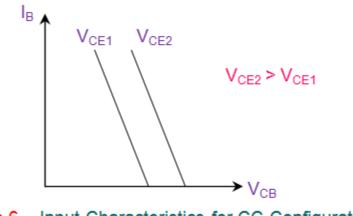

- The input characteristics for the CE configuration of transistor which illustrates the variation in  $I_B$  in accordance with  $V_{BE}$  when  $V_{CE}$  is kept constant.

- From the graph shown in Figure 10 above, the input resistance of the transistor can be obtained as

$$R_{in} = \frac{\Delta V_{BE}}{\Delta I_B} \Big|_{V_{CE}=constant}$$

Input characteristics for a common-emitter NPN transistor

- I<sub>B</sub> is microamperes compared to miliamperes of I<sub>C</sub>.

- I<sub>B</sub> will flow when V<sub>BE</sub> > 0.7V for silicon and 0.3V for germanium

- Before this value  $I_B$  is very small and no  $I_B$ .

- Base-emitter junction is forward bias

- Increasing V<sub>CE</sub> will reduce I<sub>B</sub> for different values.

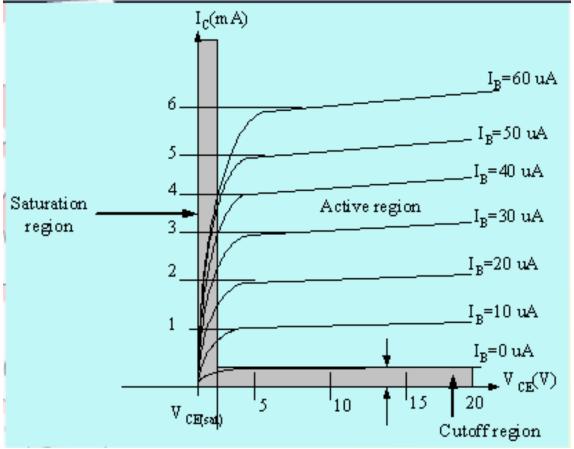

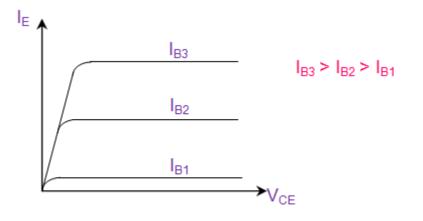

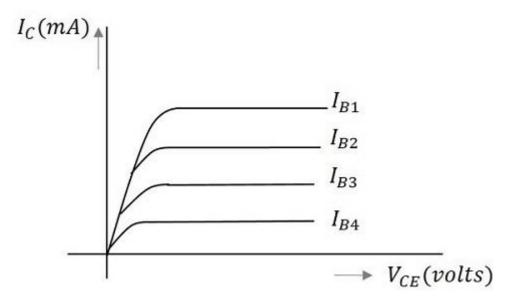

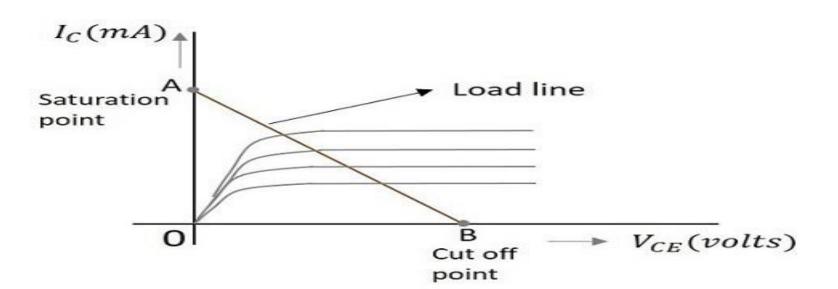

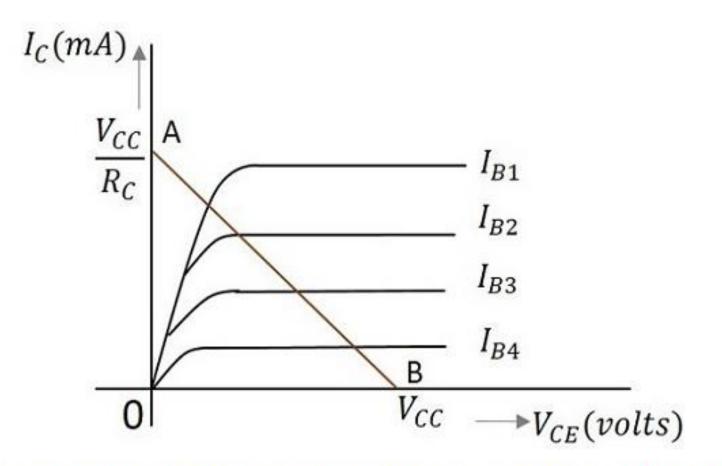

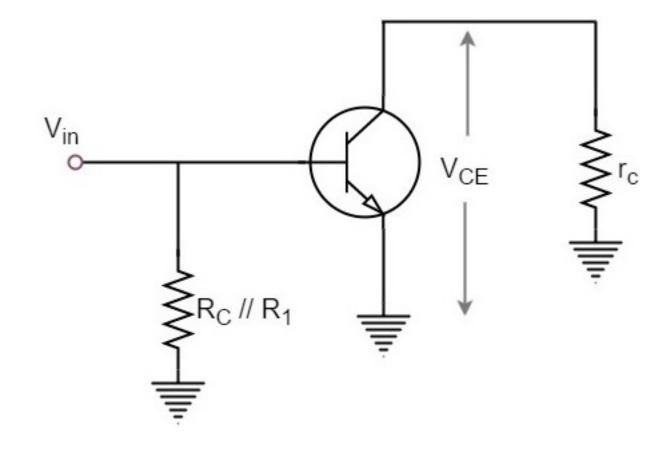

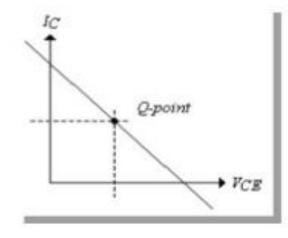

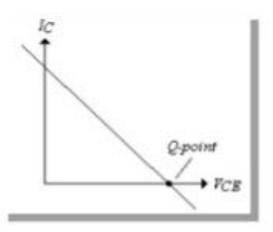

### **Output Characteristics**

The variation in I<sub>C</sub> with the changes in V<sub>CE</sub> when I<sub>B</sub> is held constant. From the graph shown, the output resistance can be obtained as:

$$R_{out} = \frac{\Delta V_{CE}}{\Delta I_C} \Big|_{I_B = constant}$$

Output characteristics for a common-emitter npn transistor

- For small V<sub>CE</sub> (V<sub>CE</sub> < V<sub>CESAT</sub>, I<sub>C</sub> increase linearly with increasing of V<sub>CE</sub>

- $V_{CE} > V_{CESAT} I_C$  not totally depends on  $V_{CE} \rightarrow$  constant  $I_C$

- $I_B(uA)$  is very small compare to  $I_C$  (mA). Small increase in  $I_B$  cause big increase in  $I_C$

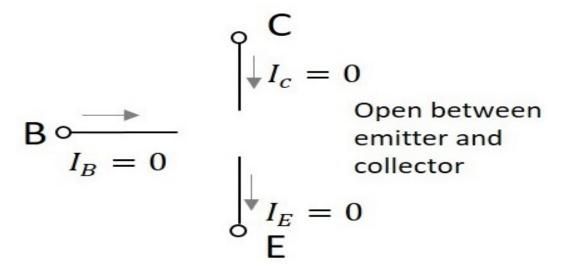

- $I_B = 0 A \rightarrow I_{CEO}$  occur.

- Noticing the value when  $\rm I_{C}=0A.$  There is still some value of current flows.

| Active<br>region                                                                                                        | Saturation<br>region                                                                                                                                                                       | Cut-off<br>region                                                                                                                                                                   |

|-------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>B-E junction is<br/>forward bias</li> <li>C-B junction is<br/>reverse bias</li> <li>can be employed</li> </ul> | <ul> <li>B-E and C-B junction<br/>is forward bias, thus<br/>the values of I<sub>B</sub> and I<sub>C</sub><br/>is too big.</li> <li>The value of V<sub>CE</sub> is<br/>so small.</li> </ul> | <ul> <li>region below I<sub>B</sub>=0µA<br/>is to be avoided if an<br/>undistorted o/p signal<br/>is required</li> <li>B-E junction and C-B<br/>junction is reverse bias</li> </ul> |

| for voltage, current<br>and power<br>amplification                                                                      | <ul> <li>Suitable region<br/>when the transistor as<br/>a logic switch.</li> <li>NOT and avoid this<br/>region when the<br/>transistor as an<br/>amplifier.</li> </ul>                     | • $I_B = 0$ , $I_C$ not zero,<br>during this condition<br>$I_C = I_{CEO}$ where is this<br>current flow when B-E<br>is reverse bias.                                                |

| 22                                                                                                                      |                                                                                                                                                                                            | c                                                                                                                                                                                   |

I<sub>CEO</sub>

в

$I_B=0$

npn

Ē

$B \circ I_B = 0$

ICEO

Ē

Base open

Collector to emitter

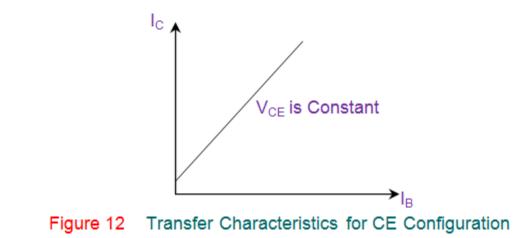

### **Current Transfer Characteristics**

• This characteristic of CE configuration shows the variation of  $I_C$  with  $I_B$  keeping  $V_{CE}$  as a constant. This ratio is referred to as commonemitter current gain and is always greater than 1. This can be mathematically given by

### Relation between $\beta$ and $\alpha$

Let us try to derive the relation between base current amplification factor and emitter current amplification factor.

$$eta = rac{\Delta I_C}{\Delta I_B}$$

$lpha = rac{\Delta I_C}{\Delta I_E}$

$I_E = I_B + I_C$

$\Delta I_E = \Delta I_B + \Delta I_C$

$\Delta I_B = \Delta I_E - \Delta I_C$

We can write

$$eta = rac{\Delta I_C}{\Delta I_E - \Delta I_C}$$

### Relation between $\beta$ and $\alpha$

Dividing by ∆l<sub>E</sub>

$$eta = rac{\Delta I_C / \Delta I_E}{rac{\Delta I_E}{\Delta I_E} - rac{\Delta I_C}{\Delta I_E}}$$

We have

$lpha = \Delta I_C / \Delta I_E$

Therefore,

$$\beta = rac{lpha}{1-lpha}$$

From the above equation, it is evident that, as α approaches 1, β reaches infinity.

Hence, the current gain in Common Emitter connection is very high. This is the reason this circuit connection is mostly used in all transistor applications.

### **Expression for Collector Current**

In the Common Emitter configuration,  $I_{\mathsf{B}}$  is the input current and  $I_{\mathsf{C}}$  is the output current. We know

$$I_E = I_B + I_C$$

And

$I_C = \alpha I_E + I_{CBO}$

$= lpha (I_B + I_C) + I_{CBO}$

$I_C(1-\alpha) = \alpha I_B + I_{CBO}$

$$I_C = rac{lpha}{1-lpha} I_B + rac{1}{1-lpha} I_{CBO}$$

If base circuit is open, i.e. if I<sub>B</sub> = 0,

The collector emitter current with base open is ICEO

$$I_{CEO} = rac{1}{1-lpha} I_{CBO}$$

# **Expression for Collector Current**

Substituting the value of this in the previous equation, we get

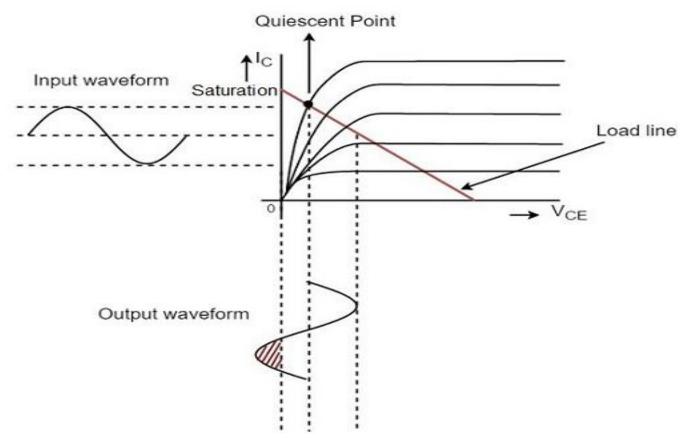

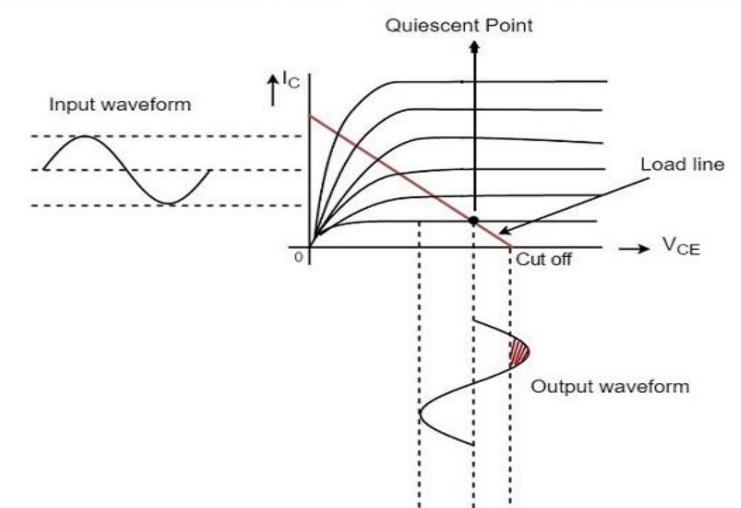

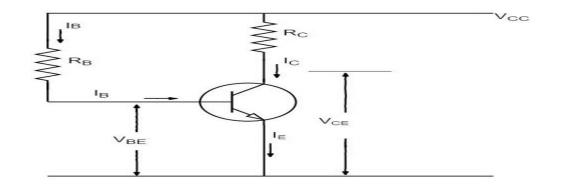

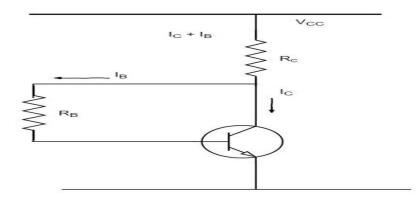

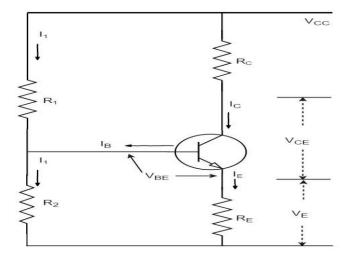

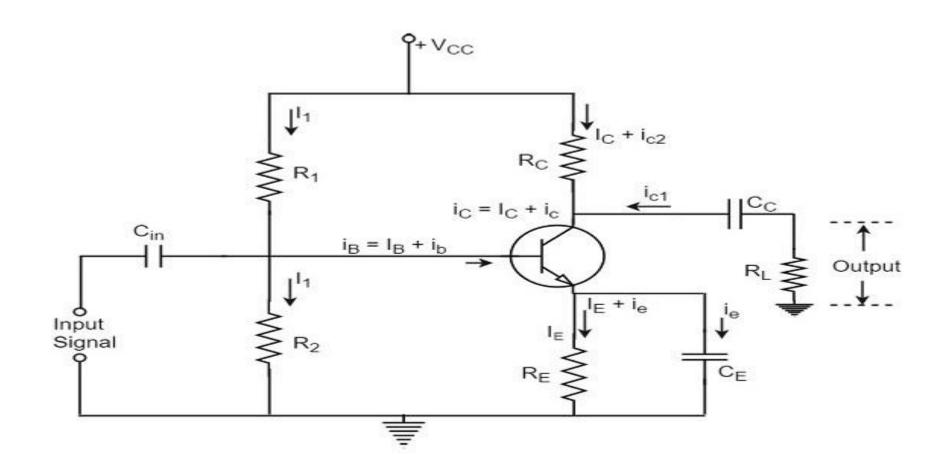

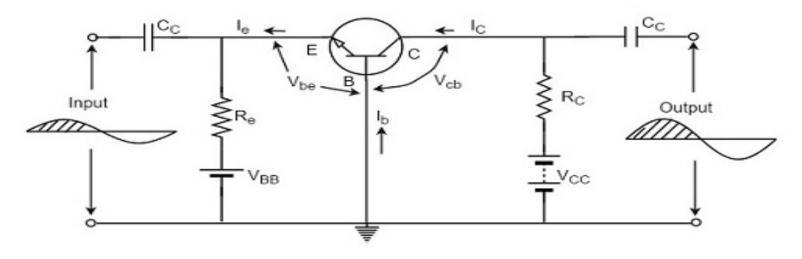

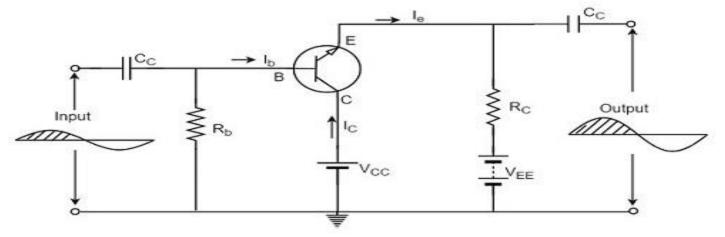

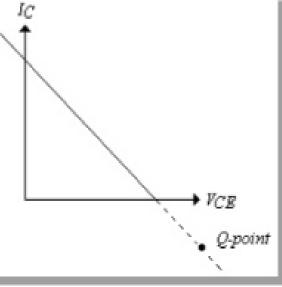

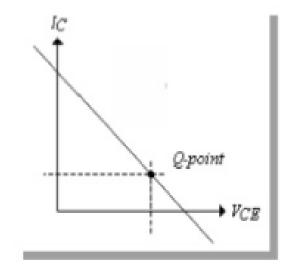

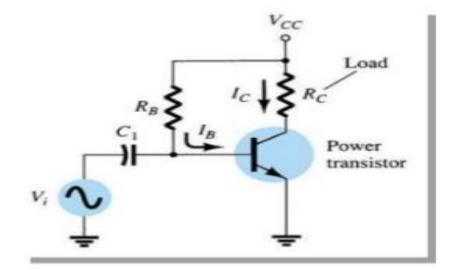

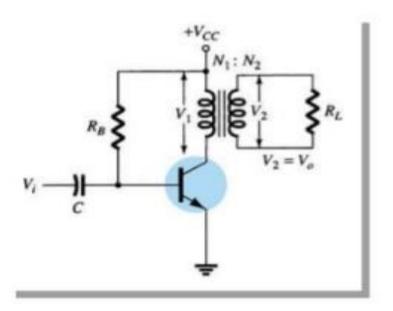

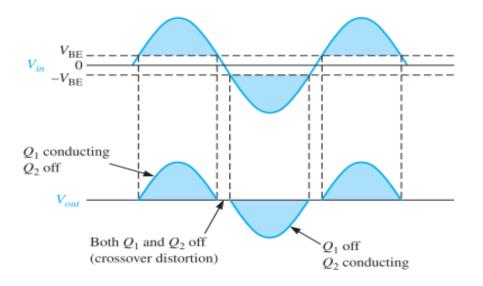

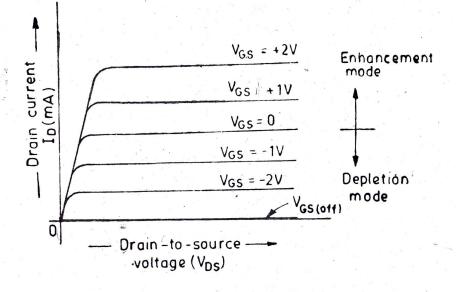

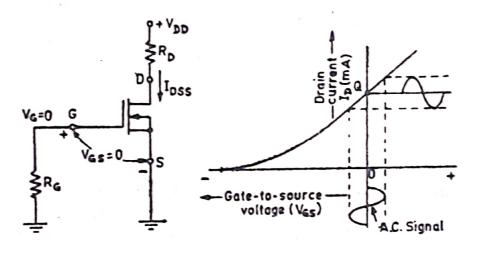

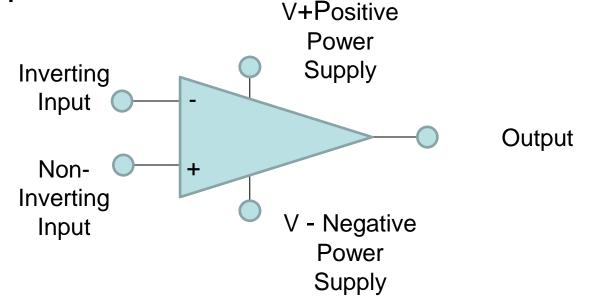

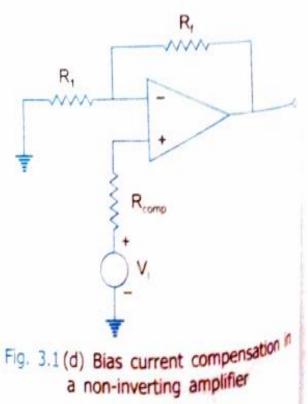

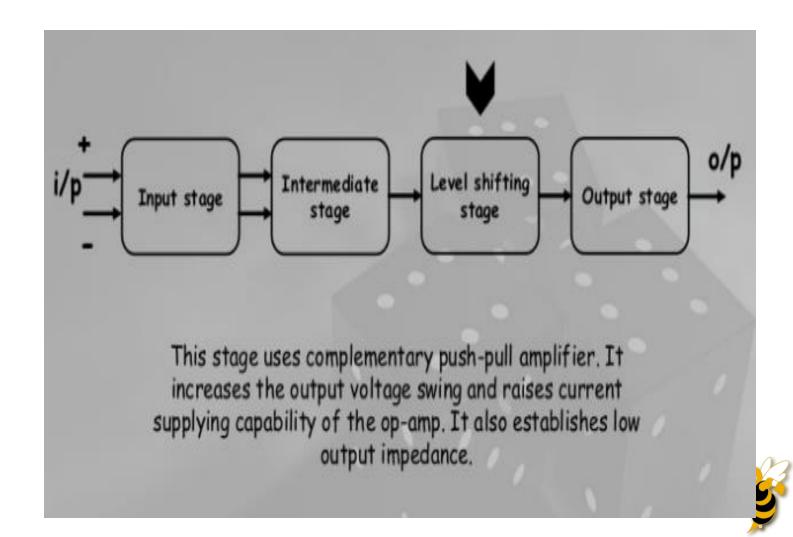

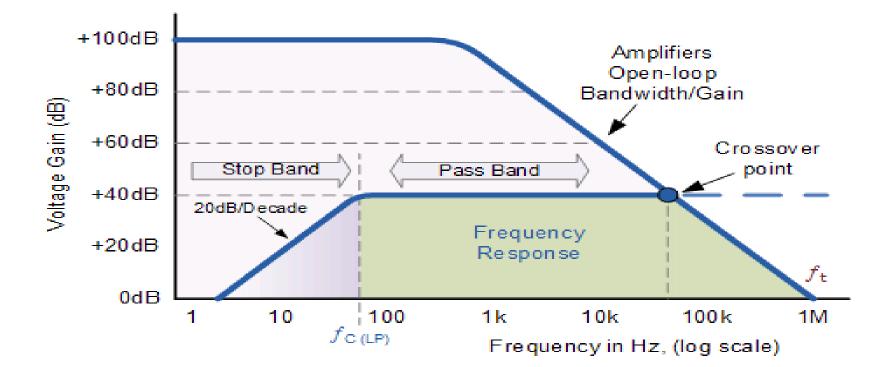

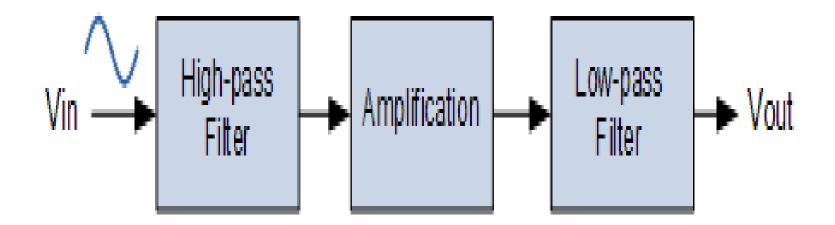

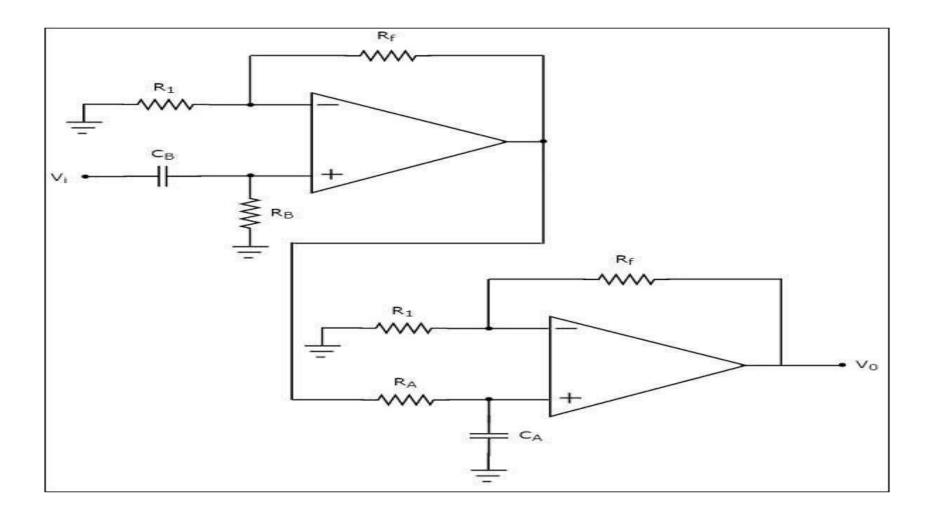

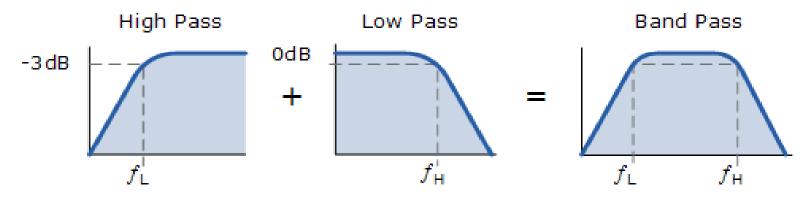

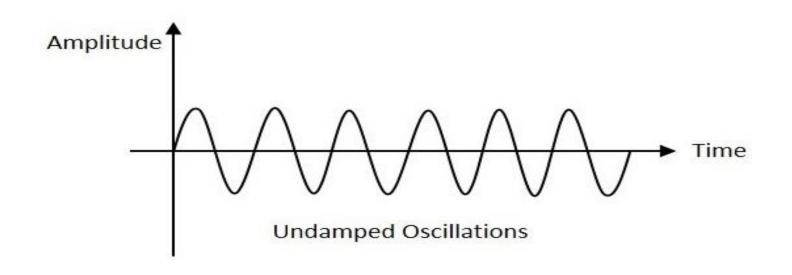

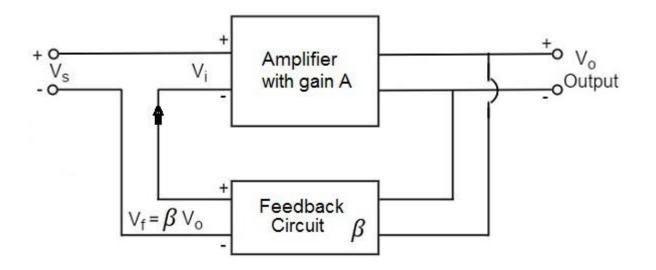

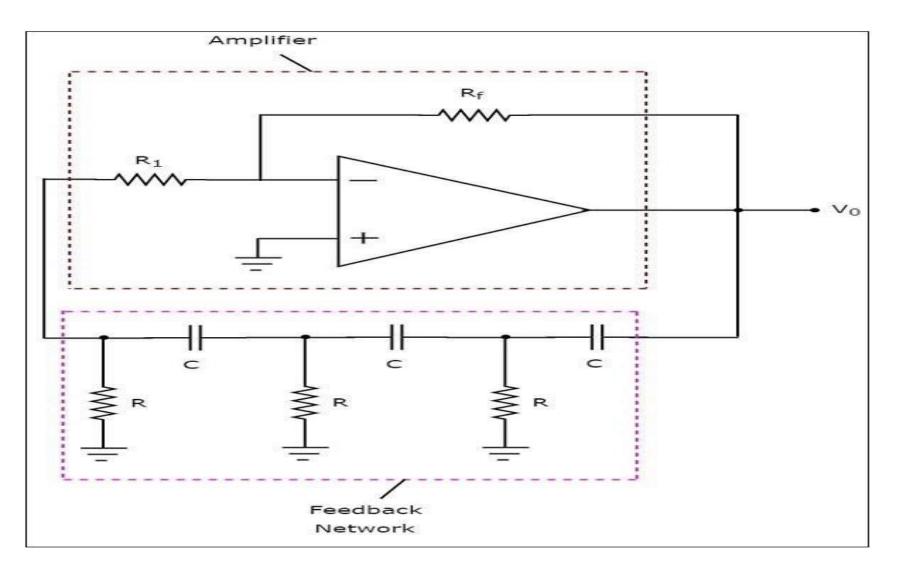

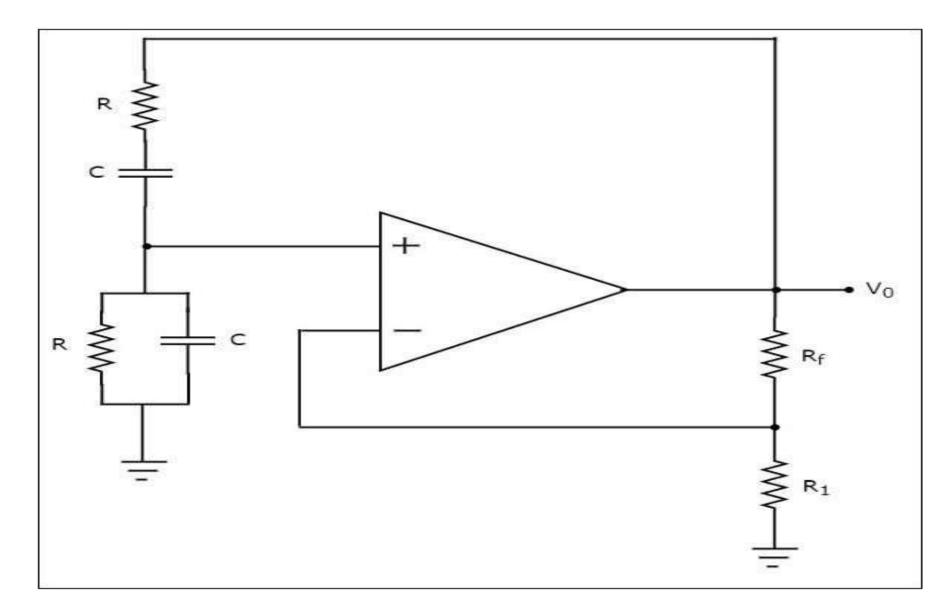

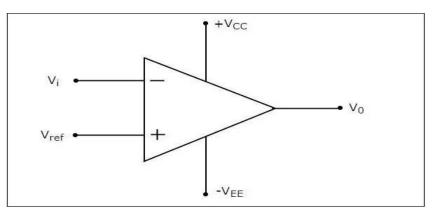

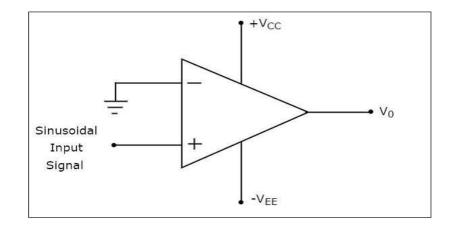

$$I_C = \frac{\alpha}{1 - \alpha} I_B + I_{CEO}$$